8-24 Vol. 3A

MULTIPLE-PROCESSOR MANAGEMENT

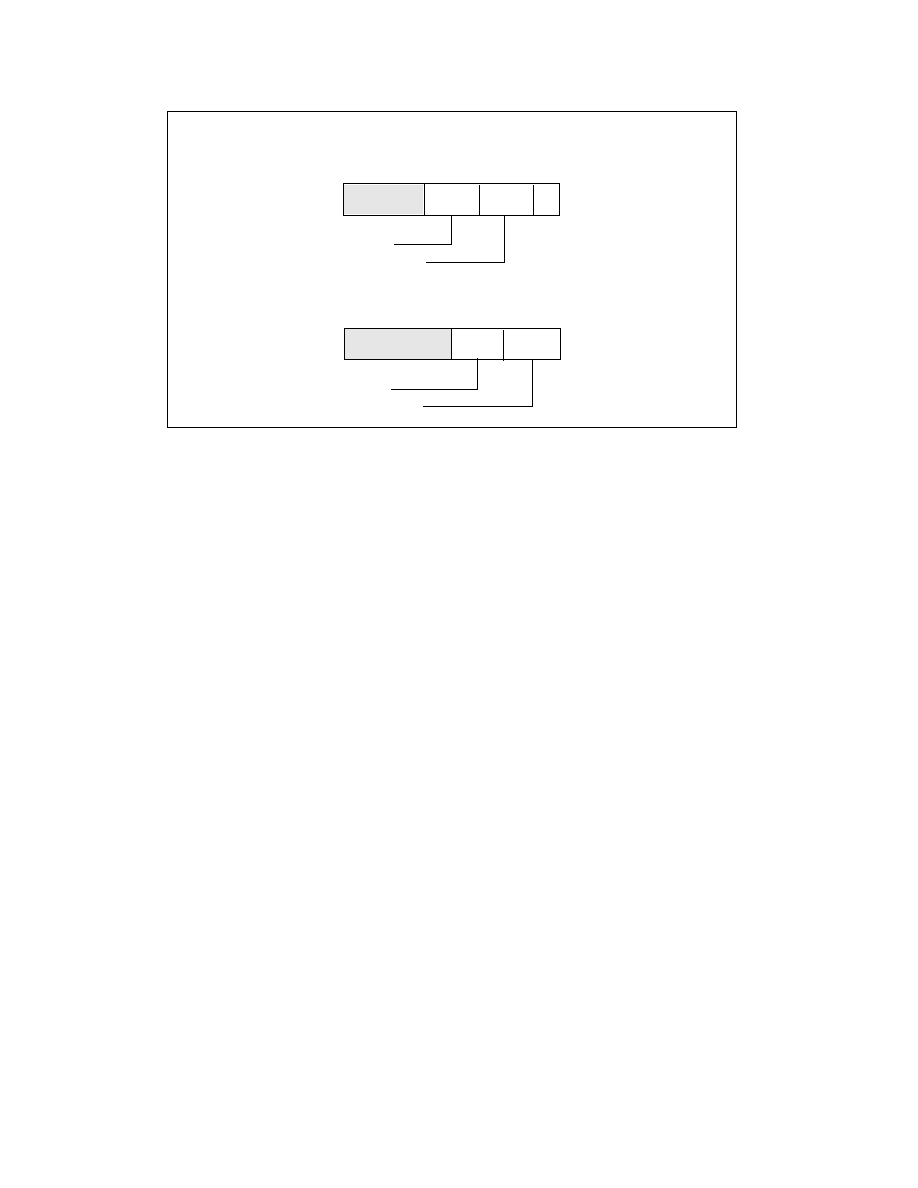

For P6 family processors, the APIC ID that is assigned to a processor during power-up and initialization is 4 bits

(see Figure 8-2). Here, bits 0 and 1 form a 2-bit processor (or socket) identifier and bits 2 and 3 form a 2-bit cluster

ID.

8.5 INTEL

®

HYPER-THREADING TECHNOLOGY AND INTEL

®

MULTI-CORE

TECHNOLOGY

Intel Hyper-Threading Technology and Intel multi-core technology are extensions to Intel 64 and IA-32 architec-

tures that enable a single physical processor to execute two or more separate code streams (called threads)

concurrently. In Intel Hyper-Threading Technology, a single processor core provides two logical processors that

share execution resources (see Section 8.7, “Intel

Hyper-Threading Technology Architecture”). In Intel multi-core

technology, a physical processor package provides two or more processor cores. Both configurations require chip-

sets and a BIOS that support the technologies.

Software should not rely on processor names to determine whether a processor supports Intel Hyper-Threading

Technology or Intel multi-core technology. Use the CPUID instruction to determine processor capability (see

Section 8.6.2, “Initializing Multi-Core Processors”).

8.6

DETECTING HARDWARE MULTI-THREADING SUPPORT AND TOPOLOGY

Use the CPUID instruction to detect the presence of hardware multi-threading support in a physical processor.

Hardware multi-threading can support several varieties of multigrade and/or Intel Hyper-Threading Technology.

CPUID instruction provides several sets of parameter information to aid software enumerating topology informa-

tion. The relevant topology enumeration parameters provided by CPUID include:

•

Hardware Multi-Threading feature flag (CPUID.1:EDX[28] = 1) — Indicates when set that the physical

package is capable of supporting Intel Hyper-Threading Technology and/or multiple cores.

•

Processor topology enumeration parameters for 8-bit APIC ID:

— Addressable IDs for Logical processors in the same Package (CPUID.1:EBX[23:16]) — Indicates

the maximum number of addressable ID for logical processors in a physical package. Within a physical

package, there may be addressable IDs that are not occupied by any logical processors. This parameter

does not represents the hardware capability of the physical processor.

6

Figure 8-2. Interpretation of APIC ID in Early MP Systems

0

Processor ID

1

7

4

3

2

Cluster

Reserved

0

Processor ID

1

7

4

3

2

5

Cluster

Reserved

APIC ID Format for Intel Xeon Processors that

APIC ID Format for P6 Family Processors

0

do not Support Intel Hyper-Threading Technology