17-38 Vol. 3B

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

•

Last Branch Record (LBR) Stack — The LBR stack consists of 8 MSRs (MSR_LASTBRANCH_0 through

MSR_LASTBRANCH_7); bits 31-0 hold the ‘from’ address, bits 63-32 hold the ‘to’ address. For Pentium M

Processors, these pairs are located at register addresses 040H-047H. See Figure 17-17.

•

Last Branch Record Top-of-Stack (TOS) Pointer — The TOS Pointer MSR contains a 3-bit pointer (bits 2-0)

to the MSR in the LBR stack that contains the most recent branch, interrupt, or exception recorded. For Pentium

M Processors, this MSR is located at register address 01C9H.

For more detail on these capabilities, see Section 17.11.3, “Last Exception Records,” and Section 35.20, “MSRs In

the Pentium M Processor.”

17.14 LAST BRANCH, INTERRUPT, AND EXCEPTION

RECORDING (P6 FAMILY PROCESSORS)

The P6 family processors provide five MSRs for recording the last branch, interrupt, or exception taken by the

processor: DEBUGCTLMSR, LastBranchToIP, LastBranchFromIP, LastExceptionToIP, and LastExceptionFromIP.

These registers can be used to collect last branch records, to set breakpoints on branches, interrupts, and excep-

tions, and to single-step from one branch to the next.

See Chapter 35, “Model-Specific Registers (MSRs),” for a detailed description of each of the last branch recording

MSRs.

17.14.1 DEBUGCTLMSR

Register

The version of the DEBUGCTLMSR register found in the P6 family processors enables last branch, interrupt, and

exception recording; taken branch breakpoints; the breakpoint reporting pins; and trace messages. This register

can be written to using the WRMSR instruction, when operating at privilege level 0 or when in real-address mode.

A protected-mode operating system procedure is required to provide user access to this register. Figure 17-18

shows the flags in the DEBUGCTLMSR register for the P6 family processors. The functions of these flags are as

follows:

•

LBR (last branch/interrupt/exception) flag (bit 0) — When set, the processor records the source and

target addresses (in the LastBranchToIP, LastBranchFromIP, LastExceptionToIP, and LastExceptionFromIP

MSRs) for the last branch and the last exception or interrupt taken by the processor prior to a debug exception

being generated. The processor clears this flag whenever a debug exception, such as an instruction or data

breakpoint or single-step trap occurs.

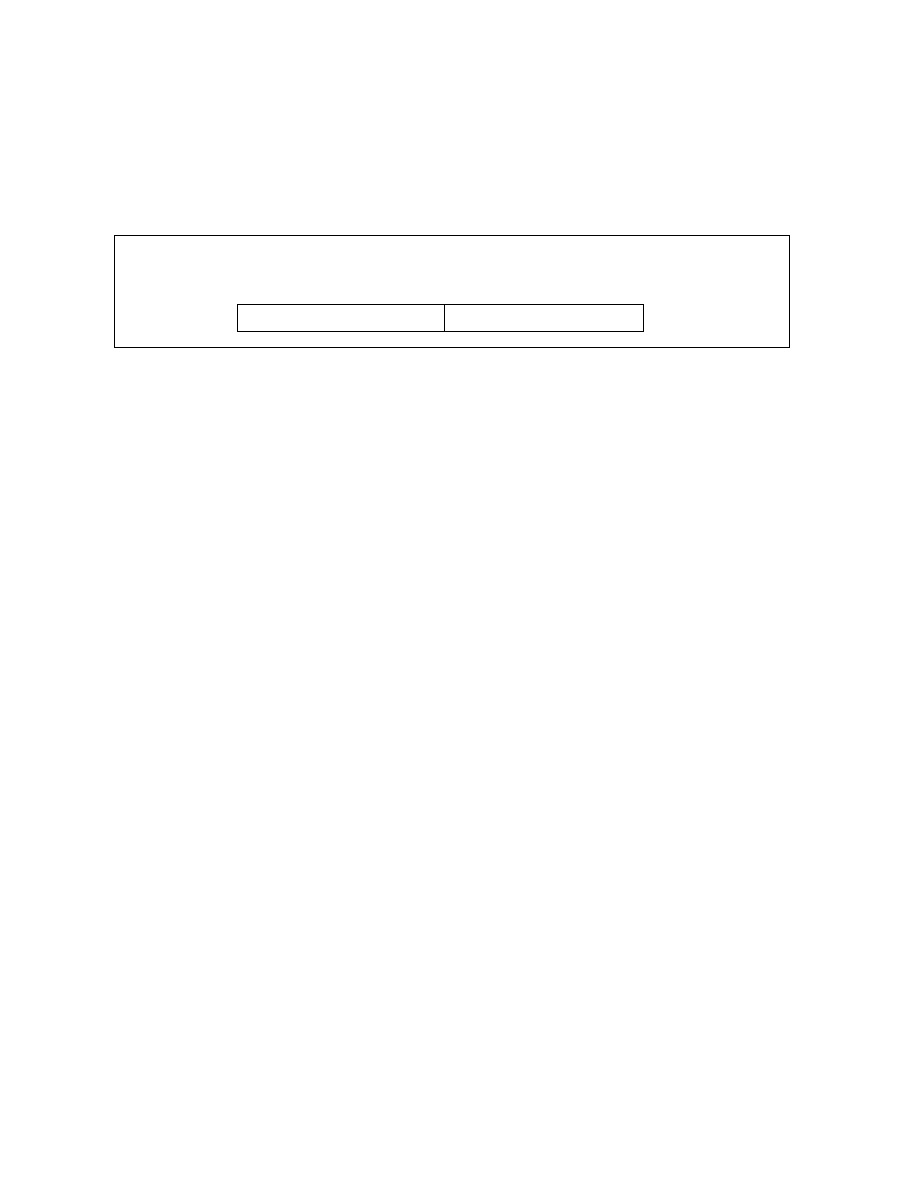

Figure 17-17. LBR Branch Record Layout for the Pentium M Processor

0

63

From Linear Address

To Linear Address

32 - 31

MSR_LASTBRANCH_0 through

MSR_LASTBRANCH_7