Vol. 3C 35-313

MODEL-SPECIFIC REGISTERS (MSRS)

35.20 MSRS IN THE PENTIUM M PROCESSOR

Model-specific registers (MSRs) for the Pentium M processor are similar to those described in Section 35.21 for P6

family processors. The following table describes new MSRs and MSRs whose behavior has changed on the Pentium

M processor.

31:0

DS Buffer Management Area

Linear address of the first byte of the DS buffer management area.

63:32

Reserved.

C000_

0080H

IA32_EFER

Unique

See Table 35-2.

10:0

Reserved.

11

Execute Disable Bit Enable

63:12

Reserved.

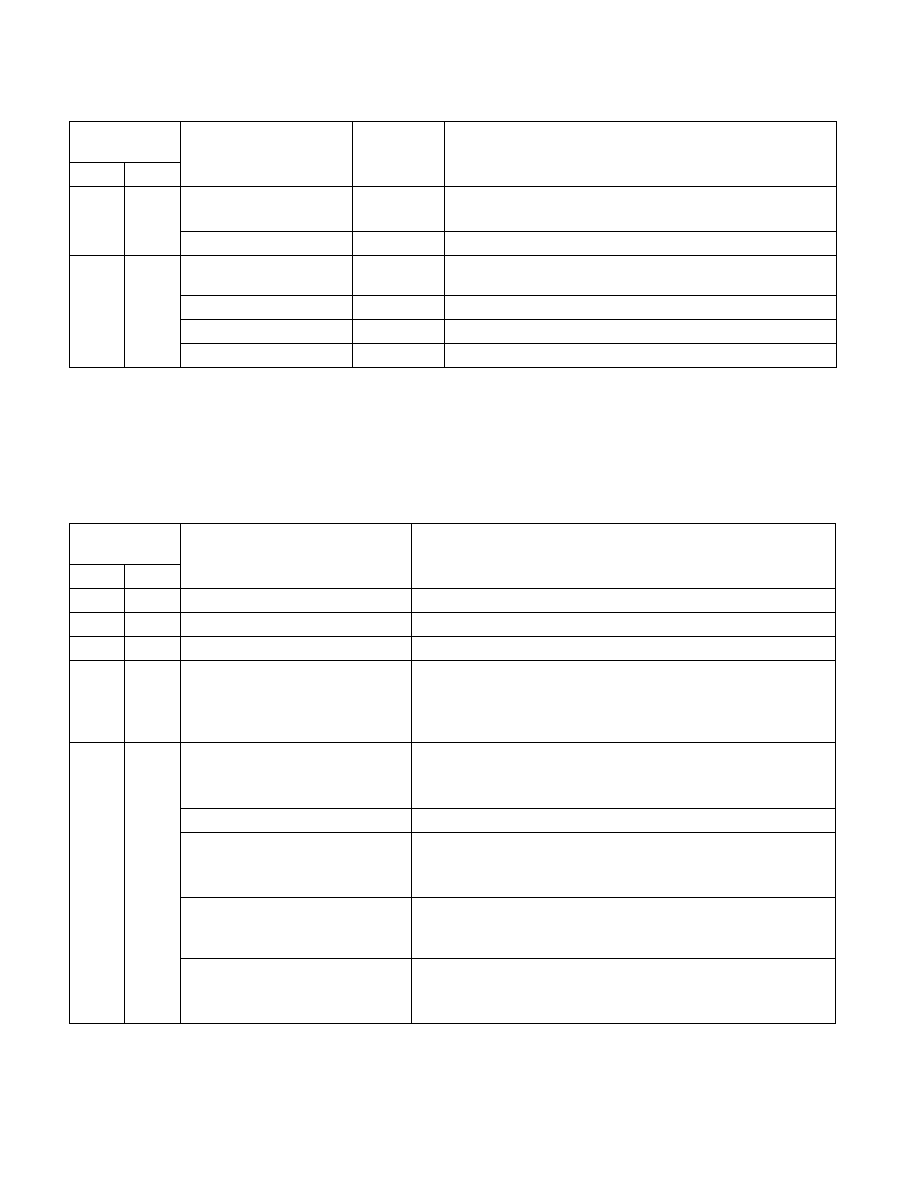

Table 35-45. MSRs in Pentium M Processors

Register

Address

Register Name

Bit Description

Hex

Dec

0H

0

P5_MC_ADDR

See Section 35.22, “MSRs in Pentium Processors.”

1H

1

P5_MC_TYPE

See Section 35.22, “MSRs in Pentium Processors.”

10H

16

IA32_TIME_STAMP_COUNTER

See Section 17.15, “Time-Stamp Counter,” and see Table 35-2.

17H

23

IA32_PLATFORM_ID

Platform ID (R)

See Table 35-2.

The operating system can use this MSR to determine “slot” information

for the processor and the proper microcode update to load.

2AH

42

MSR_EBL_CR_POWERON

Processor Hard Power-On Configuration

(R/W) Enables and disables processor features.

(R) Indicates current processor configuration.

0

Reserved.

1

Data Error Checking Enable (R)

0 = Disabled

Always 0 on the Pentium M processor.

2

Response Error Checking Enable (R)

0 = Disabled

Always 0 on the Pentium M processor.

3

MCERR# Drive Enable (R)

0 = Disabled

Always 0 on the Pentium M processor.

Table 35-44. MSRs in Intel® Core™ Solo, Intel® Core™ Duo Processors, and Dual-Core Intel® Xeon® Processor LV

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec