17-26 Vol. 3B

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

•

Last Branch Record Top-of-Stack (TOS) Pointer — The lowest significant 2 bits of the TOS Pointer MSR

(MSR_LASTBRANCH_TOS, address 1C9H) contains a pointer to the MSR in the LBR stack that contains the most

recent branch, interrupt, or exception recorded.

Eight pairs of MSRs are supported in the LBR stack for 45 nm and 32 nm Intel Atom processors:

•

Last Branch Record (LBR) Stack

— MSR_LASTBRANCH_0_FROM_IP (address 40H) through MSR_LASTBRANCH_7_FROM_IP (address 47H)

store source addresses

— MSR_LASTBRANCH_0_TO_IP (address 60H) through MSR_LASTBRANCH_7_TO_IP (address 67H) store

destination addresses

•

Last Branch Record Top-of-Stack (TOS) Pointer — The lowest significant 3 bits of the TOS Pointer MSR

(MSR_LASTBRANCH_TOS, address 1C9H) contains a pointer to the MSR in the LBR stack that contains the most

recent branch, interrupt, or exception recorded.

The address format written in the FROM_IP/TO_IP MSRS may differ between processors. Software should query

IA32_PERF_CAPABILITIES[5:0] and consult Section 17.4.8.1. The behavior of the MSR_LER_TO_LIP and the

MSR_LER_FROM_LIP MSRs corresponds to that of the LastExceptionToIP and LastExceptionFromIP MSRs found in

P6 family processors.

17.5.2

LBR Stack in Intel Atom Processors based on the Silvermont Microarchitecture

The last branch record stack and top-of-stack (TOS) pointer MSRs are supported in Intel Atom processors based on

the Silvermont and Airmont microarchitectures. Eight pairs of MSRs are supported in the LBR stack.

LBR filtering is supported. Filtering of LBRs based on a combination of CPL and branch type conditions is supported.

When LBR filtering is enabled, the LBR stack only captures the subset of branches that are specified by

MSR_LBR_SELECT. The layout of MSR_LBR_SELECT is described in Table 17-11.

17.6

LAST BRANCH, CALL STACK, INTERRUPT, AND EXCEPTION RECORDING

FOR PROCESSORS BASED ON GOLDMONT MICROARCHITECTURE

Next generation Intel Atom processors are based on the Goldmont microarchitecture. Processors based on the

Goldmont microarchitecture extend the capabilities described in Section 17.5.2 with the following enhancements:

•

Supports new LBR format encoding 00110b in IA32_PERF_CAPABILITIES[5:0].

•

Size of LBR stack increased to 32. Each entry includes MSR_LASTBRANCH_x_FROM_IP (address 0x680..0x69f)

and MSR_LASTBRANCH_x_TO_IP (address 0x6c0..0x6df).

• LBR call stack filtering supported. The layout of MSR_LBR_SELECT is described in Table 17-13.

• Elapsed cycle information is added to MSR_LASTBRANCH_x_TO_IP. Format is shown in Table 17-7.

•

Misprediction info is reported in the upper bits of MSR_LASTBRANCH_x_FROM_IP. MISPRED bit format is

• Streamlined Freeze_LBRs_On_PMI operation; see Section 17.10.2.

• LBR MSRs are cleared when software requests C6 or deeper sleep-state; see Section 17.10.3.

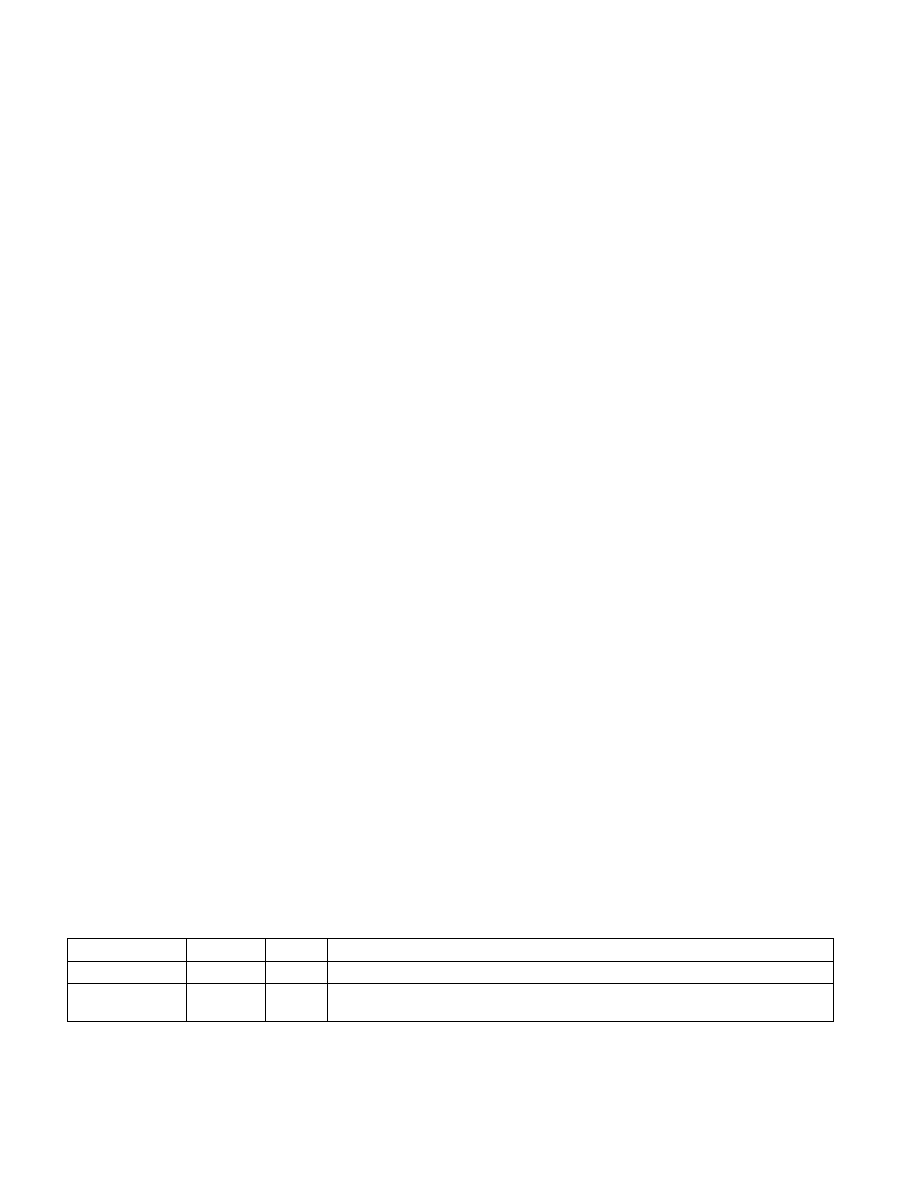

Table 17-7. MSR_LASTBRANCH_x_TO_IP for the Goldmont Microarchitecture

Bit Field

Bit Offset

Access

Description

Data

47:0

R/O

This is the “branch to“ address. See Section 17.4.8.1 for address format.

Cycle Count

(Saturating)

63:48

R/0

Elapsed core clocks since last update to the LBR stack.