17-32 Vol. 3B

DEBUG, BRANCH PROFILE, TSC, AND RESOURCE MONITORING FEATURES

17.10.2 Streamlined Freeze_LBRs_On_PMI Operation

The capability to freeze the content of LBR to maintain recorded data quality continues to use the same interface

IA32_DEBUGCTL.Freeze_LBRs_ON_PMI. Architectural performance monitoring version 4 and above supports a

streamlined Freeze_LBRs_ON_PMI operation for PMI service routine that replaces the legacy

Freeze_LBRs_ON_PMI operation (see Section 17.4.7).

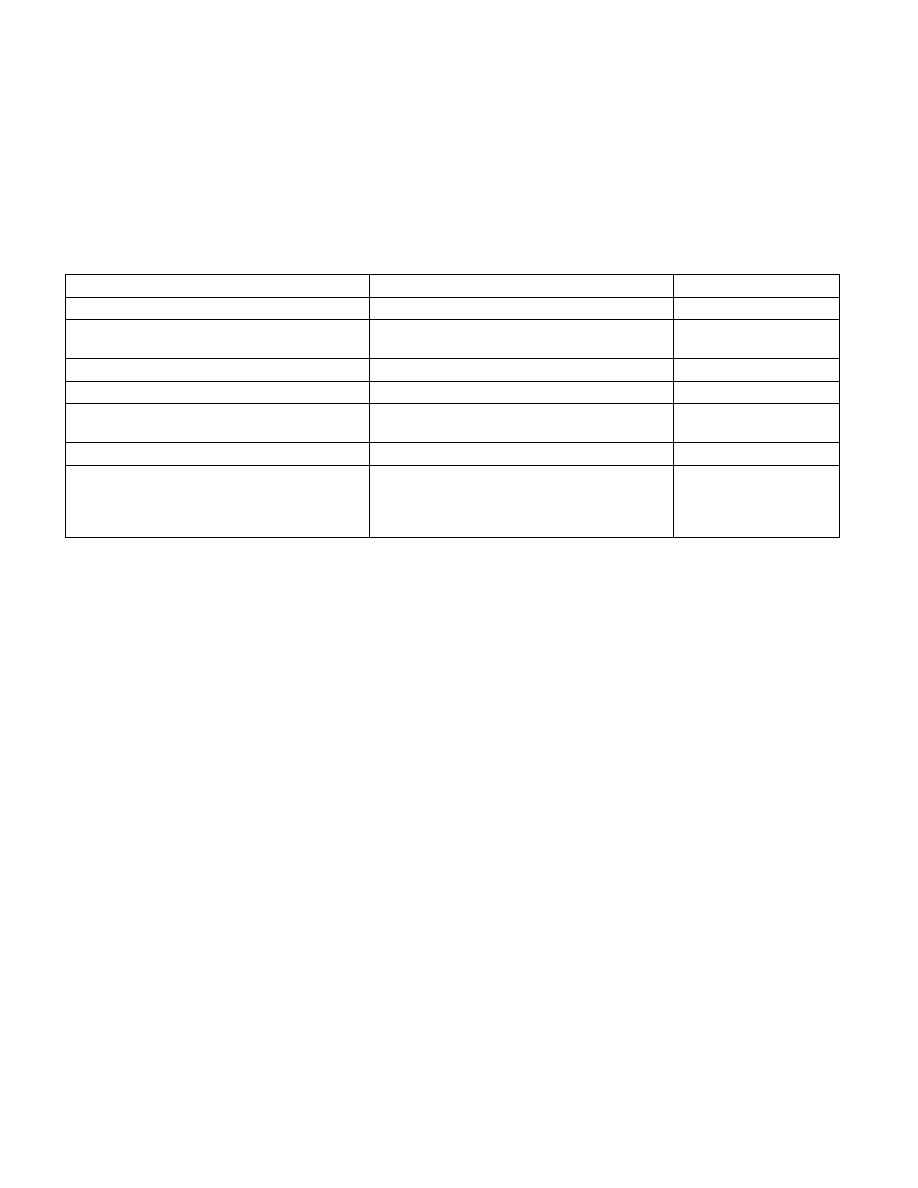

Table 17-17 compares the interaction of the processor with the PMI handler.

Table 17-17. Legacy and Streamlined Operation with Freeze_LBRs_On_PMI = 1, Buffer Full

17.10.3 LBR Behavior and Deep C-State

When MWAIT is used to request a C-state that is numerically higher than C1, then LBR state may be initialized to

zero depending on optimized “waiting” state that is selected by the processor The affected LBR states include the

FROM, TO, INFO, LAST_BRANCH, LER and LBR_TOS registers. The LBR enable bit and LBR_FROZEN bit are not

affected. The LBR-time of the first LBR record inserted after an exit from such a C-state request will be zero.

17.11 LAST BRANCH, INTERRUPT, AND EXCEPTION RECORDING (PROCESSORS

BASED ON INTEL NETBURST® MICROARCHITECTURE)

Pentium 4 and Intel Xeon processors based on Intel NetBurst microarchitecture provide the following methods for

recording taken branches, interrupts and exceptions:

•

Store branch records in the last branch record (LBR) stack MSRs for the most recent taken branches,

interrupts, and/or exceptions in MSRs. A branch record consist of a branch-from and a branch-to instruction

address.

•

Send the branch records out on the system bus as branch trace messages (BTMs).

•

Log BTMs in a memory-resident branch trace store (BTS) buffer.

To support these functions, the processor provides the following MSRs and related facilities:

•

MSR_DEBUGCTLA MSR — Enables last branch, interrupt, and exception recording; single-stepping on taken

branches; branch trace messages (BTMs); and branch trace store (BTS). This register is named DebugCtlMSR

in the P6 family processors.

•

Debug store (DS) feature flag (CPUID.1:EDX.DS[bit 21]) — Indicates that the processor provides the

debug store (DS) mechanism, which allows BTMs to be stored in a memory-resident BTS buffer.

Legacy Freeze_LBRs_On_PMI

Streamlined Freeze_LBRs_On_PMI

Comment

Processor freezes the LBR stack on PEBS buffer full Processor freezes the LBR stack on PEBS buffer full Unchanged

Processor clears IA32_DEBUGCTRL.LBR (0x1D9)

Processor set

IA32_PERF_GLOBAL_STATUS.LBR_Frz

dbgmask = RDMSR(0x1D9)

mask = RDMSR(0x38E)

Handler services the PMI

Handler services the PMI

Unchanged

Updates dbgmask to include LBR for subsequent

write to IA32_DEBUGCTL

Handler writes mask into

IA32_PERF_GLOBAL_OVF_RESET (0x390)

NA

Processor clears IA32_PERF_GLOBAL_STATUS

Handler writes dbgmask to re-enables

IA32_DEBUGCTL.LBR

NA

Prevents race condition of

MSR 0x1D9 being updated

by the processor and

handler