Vol. 3A 10-25

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

priority for each logical processor in the system. The chipset saves this information and uses it to choose the lowest

priority processor when an interrupt is received.

For systems based on P6 family processors, the processor priority used in lowest-priority arbitration is contained in

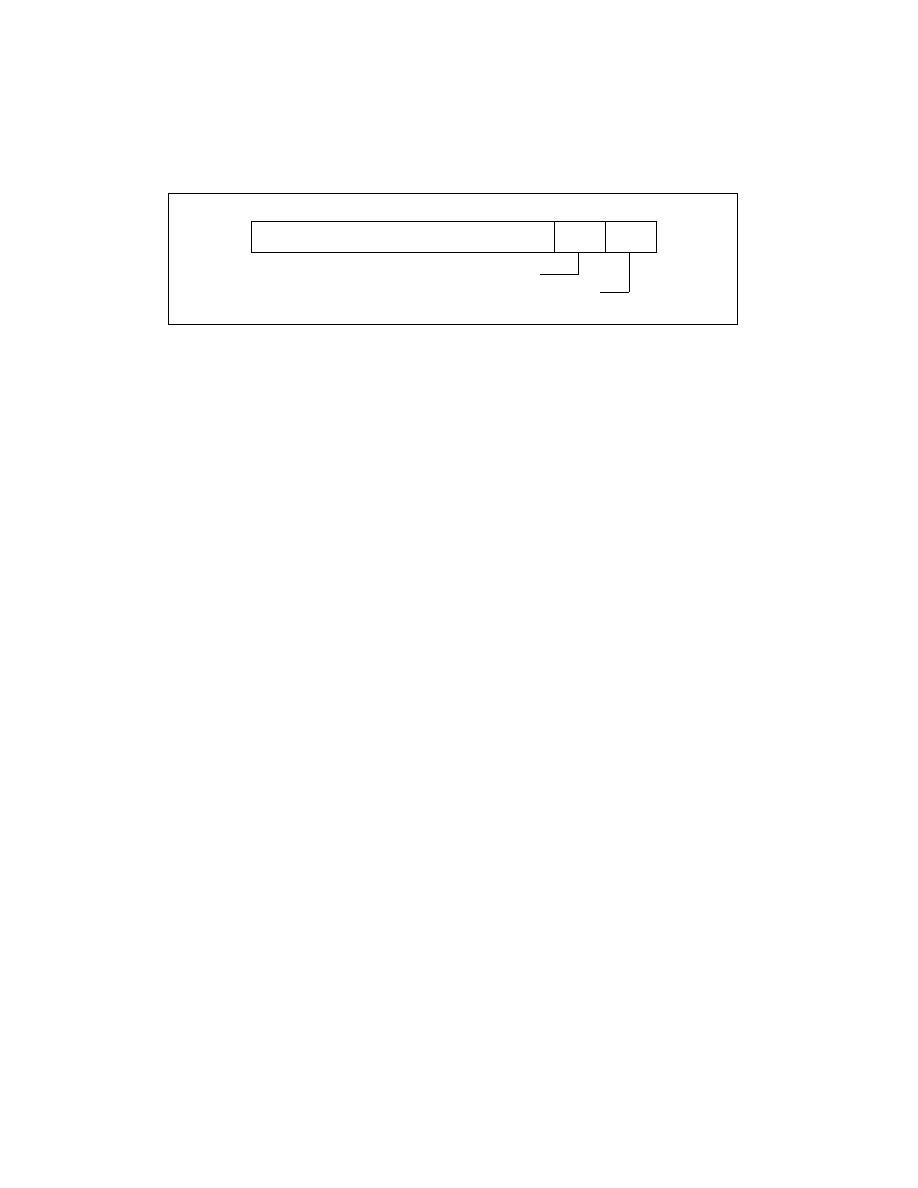

the arbitration priority register (APR) in each local APIC. Figure 10-15 shows the layout of the APR.

The APR value is computed as follows:

IF (TPR[7:4]

≥

IRRV[7:4]) AND (TPR[7:4]

>

ISRV[7:4])

THEN

APR[7:0]

←

TPR[7:0]

ELSE

APR[7:4]

←

max(TPR[7:4] AND ISRV[7:4], IRRV[7:4])

APR[3:0]

←

0.

Here, the TPR value is the task priority value in the TPR (see Figure 10-18), the IRRV value is the vector number

for the highest priority bit that is set in the IRR (see Figure 10-20) or 00H (if no IRR bit is set), and the ISRV value

is the vector number for the highest priority bit that is set in the ISR (see Figure 10-20). Following arbitration

among the destination processors, the processor with the lowest value in its APR handles the IPI and the other

processors ignore it.

(P6 family and Pentium processors.) For these processors, if a focus processor exists, it may accept the interrupt,

regardless of its priority. A processor is said to be the focus of an interrupt if it is currently servicing that interrupt

or if it has a pending request for that interrupt. For Intel Xeon processors, the concept of a focus processor is not

supported.

In operating systems that use the lowest priority delivery mode but do not update the TPR, the TPR information

saved in the chipset will potentially cause the interrupt to be always delivered to the same processor from the

logical set. This behavior is functionally backward compatible with the P6 family processor but may result in unex-

pected performance implications.

10.6.3

IPI Delivery and Acceptance

When the low double-word of the ICR is written to, the local APIC creates an IPI message from the information

contained in the ICR and sends the message out on the system bus (Pentium 4 and Intel Xeon processors) or the

APIC bus (P6 family and Pentium processors). The manner in which these IPIs are handled after being issues in

described in Section 10.8, “Handling Interrupts.”

10.7

SYSTEM AND APIC BUS ARBITRATION

When several local APICs and the I/O APIC are sending IPI and interrupt messages on the system bus (or APIC

bus), the order in which the messages are sent and handled is determined through bus arbitration.

For the Pentium 4 and Intel Xeon processors, the local and I/O APICs use the arbitration mechanism defined for the

system bus to determine the order in which IPIs are handled. This mechanism is non-architectural and cannot be

controlled by software.

Figure 10-15. Arbitration Priority Register (APR)

31

0

7

8

Reserved

Address: FEE0 0090H

Value after reset: 0H

Arbitration Priority Sub-Class

Arbitration Priority Class

4 3