10-26 Vol. 3A

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

For the P6 family and Pentium processors, the local and I/O APICs use an APIC-based arbitration mechanism to

determine the order in which IPIs are handled. Here, each local APIC is given an arbitration priority of from 0 to 15,

which the I/O APIC uses during arbitration to determine which local APIC should be given access to the APIC bus.

The local APIC with the highest arbitration priority always wins bus access. Upon completion of an arbitration

round, the winning local APIC lowers its arbitration priority to 0 and the losing local APICs each raise theirs by 1.

The current arbitration priority for a local APIC is stored in a 4-bit, software-transparent arbitration ID (Arb ID)

register. During reset, this register is initialized to the APIC ID number (stored in the local APIC ID register). The

INIT level-deassert IPI, which is issued with and ICR command, can be used to resynchronize the arbitration prior-

ities of the local APICs by resetting Arb ID register of each agent to its current APIC ID value. (The Pentium 4 and

Intel Xeon processors do not implement the Arb ID register.)

Section 10.10, “APIC Bus Message Passing Mechanism and Protocol (P6 Family, Pentium Processors),” describes the

APIC bus arbitration protocols and bus message formats, while Section 10.6.1, “Interrupt Command Register

(ICR),” describes the INIT level de-assert IPI message.

Note that except for the SIPI IPI (see Section 10.6.1, “Interrupt Command Register (ICR)”), all bus messages that

fail to be delivered to their specified destination or destinations are automatically retried. Software should avoid

situations in which IPIs are sent to disabled or nonexistent local APICs, causing the messages to be resent repeat-

edly. Additionally, interrupt sources that target the APIC should be masked or changed to no longer target the APIC.

10.8 HANDLING

INTERRUPTS

When a local APIC receives an interrupt from a local source, an interrupt message from an I/O APIC, or and IPI, the

manner in which it handles the message depends on processor implementation, as described in the following

sections.

10.8.1

Interrupt Handling with the Pentium 4 and Intel Xeon Processors

With the Pentium 4 and Intel Xeon processors, the local APIC handles the local interrupts, interrupt messages, and

IPIs it receives as follows:

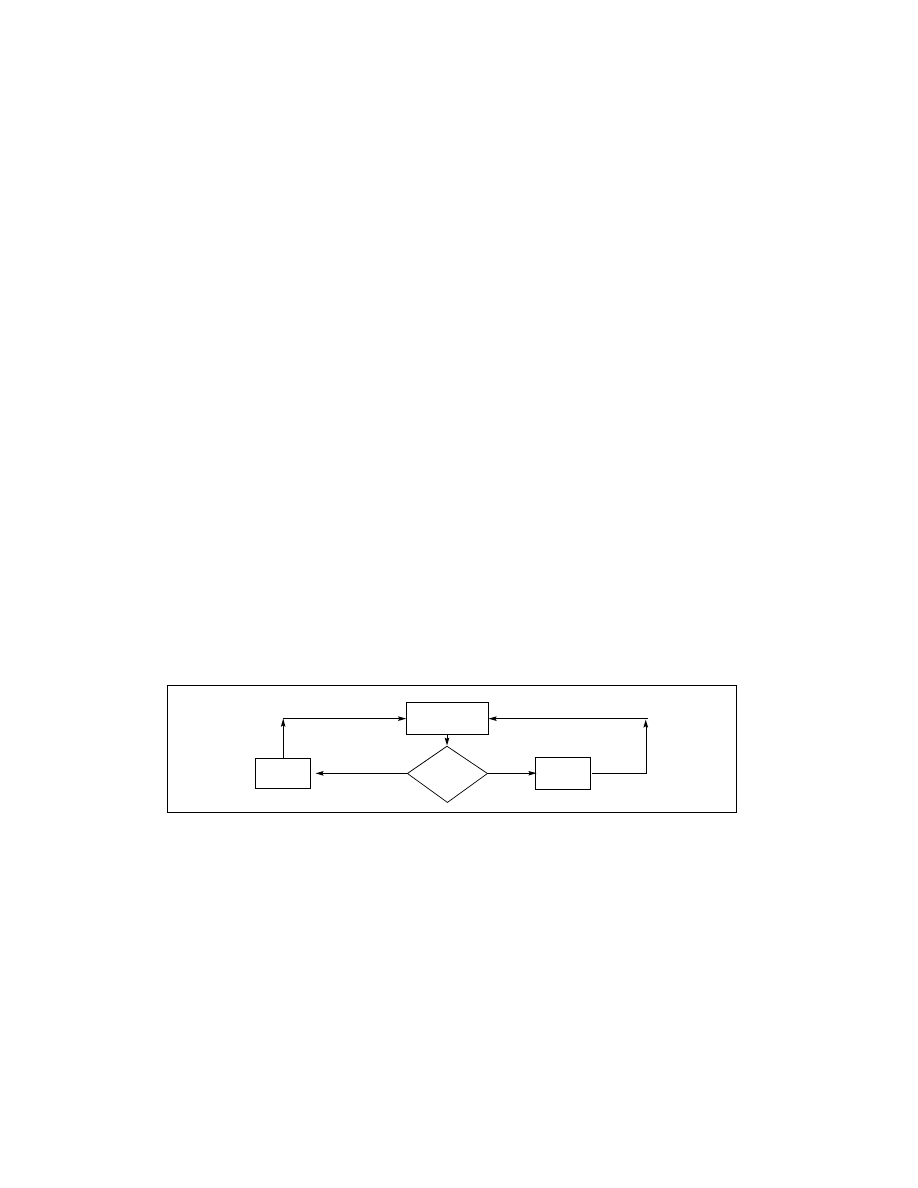

1. It determines if it is the specified destination or not (see Figure 10-16). If it is the specified destination, it

accepts the message; if it is not, it discards the message.

2. If the local APIC determines that it is the designated destination for the interrupt and if the interrupt request is

an NMI, SMI, INIT, ExtINT, or SIPI, the interrupt is sent directly to the processor core for handling.

3. If the local APIC determines that it is the designated destination for the interrupt but the interrupt request is

not one of the interrupts given in step 2, the local APIC sets the appropriate bit in the IRR.

4. When interrupts are pending in the IRR register, the local APIC dispatches them to the processor one at a time,

based on their priority and the current processor priority in the PPR (see Section 10.8.3.1, “Task and Processor

Priorities”).

5. When a fixed interrupt has been dispatched to the processor core for handling, the completion of the handler

routine is indicated with an instruction in the instruction handler code that writes to the end-of-interrupt (EOI)

register in the local APIC (see Section 10.8.5, “Signaling Interrupt Servicing Completion”). The act of writing to

the EOI register causes the local APIC to delete the interrupt from its ISR queue and (for level-triggered

Figure 10-16. Interrupt Acceptance Flow Chart for the Local APIC (Pentium 4 and Intel Xeon Processors)

Wait to Receive

Bus Message

Belong to

Destination?

Discard

Message

No

Accept

Message

Yes