10-30 Vol. 3A

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

If more than one interrupt is generated with the same vector number, the local APIC can set the bit for the vector

both in the IRR and the ISR. This means that for the Pentium 4 and Intel Xeon processors, the IRR and ISR can

queue two interrupts for each interrupt vector: one in the IRR and one in the ISR. Any additional interrupts issued

for the same interrupt vector are collapsed into the single bit in the IRR.

For the P6 family and Pentium processors, the IRR and ISR registers can queue no more than two interrupts per

interrupt vector and will reject other interrupts that are received within the same vector.

If the local APIC receives an interrupt with an interrupt-priority class higher than that of the interrupt currently in

service, and interrupts are enabled in the processor core, the local APIC dispatches the higher priority interrupt to

the processor immediately (without waiting for a write to the EOI register). The currently executing interrupt

handler is then interrupted so the higher-priority interrupt can be handled. When the handling of the higher-priority

interrupt has been completed, the servicing of the interrupted interrupt is resumed.

The trigger mode register (TMR) indicates the trigger mode of the interrupt (see Figure 10-20). Upon acceptance

of an interrupt into the IRR, the corresponding TMR bit is cleared for edge-triggered interrupts and set for level-

triggered interrupts. If a TMR bit is set when an EOI cycle for its corresponding interrupt vector is generated, an EOI

message is sent to all I/O APICs.

10.8.5

Signaling Interrupt Servicing Completion

For all interrupts except those delivered with the NMI, SMI, INIT, ExtINT, the start-up, or INIT-Deassert delivery

mode, the interrupt handler must include a write to the end-of-interrupt (EOI) register (see Figure 10-21). This

write must occur at the end of the handler routine, sometime before the IRET instruction. This action indicates that

the servicing of the current interrupt is complete and the local APIC can issue the next interrupt from the ISR.

Upon receiving an EOI, the APIC clears the highest priority bit in the ISR and dispatches the next highest priority

interrupt to the processor. If the terminated interrupt was a level-triggered interrupt, the local APIC also sends an

end-of-interrupt message to all I/O APICs.

System software may prefer to direct EOIs to specific I/O APICs rather than having the local APIC send end-of-

interrupt messages to all I/O APICs.

Software can inhibit the broadcast of EOI message by setting bit 12 of the Spurious Interrupt Vector Register (see

Section 10.9). If this bit is set, a broadcast EOI is not generated on an EOI cycle even if the associated TMR bit indi-

cates that the current interrupt was level-triggered. The default value for the bit is 0, indicating that EOI broadcasts

are performed.

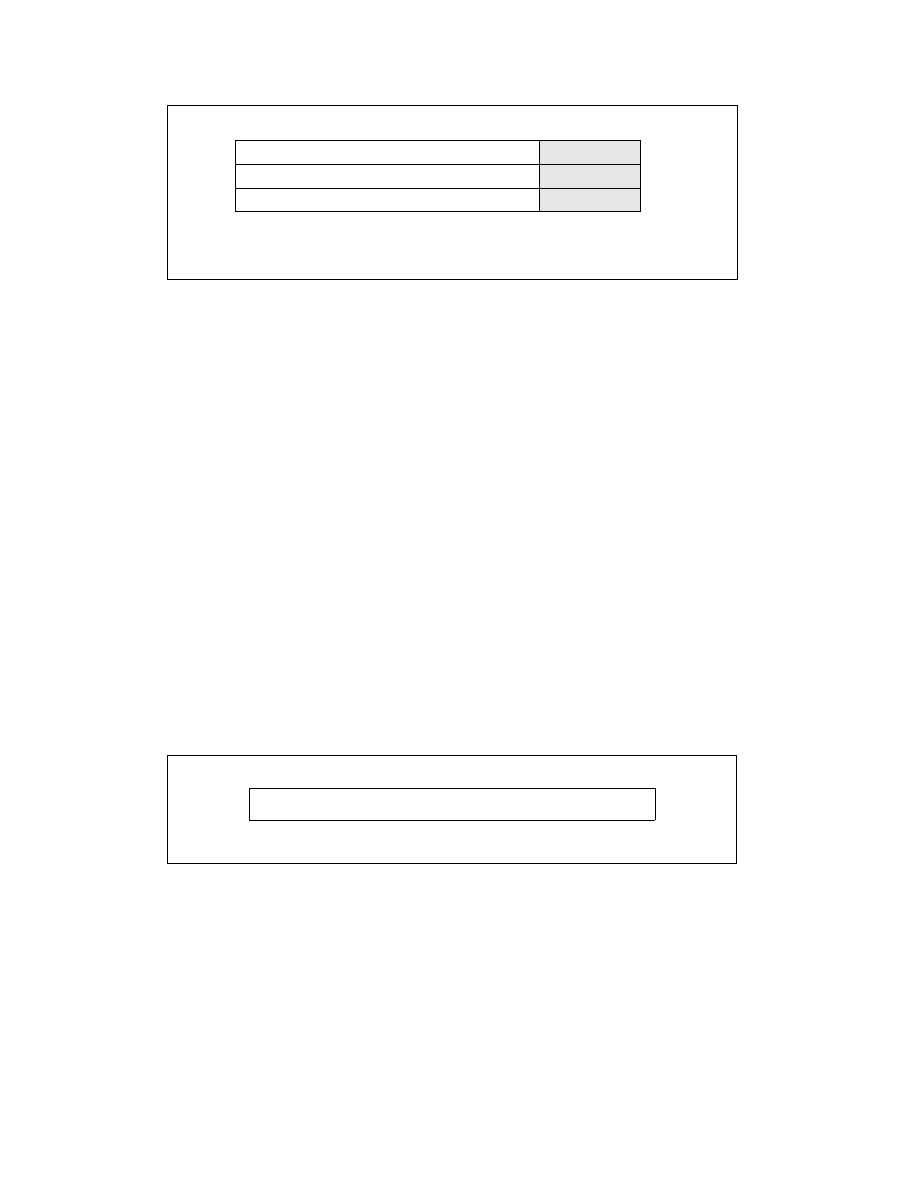

Figure 10-20. IRR, ISR and TMR Registers

Figure 10-21. EOI Register

255

0

Reserved

Addresses: IRR FEE0 0200H - FEE0 0270H

Value after reset: 0H

16 15

IRR

Reserved

ISR

Reserved

TMR

ISR FEE0 0100H - FEE0 0170H

TMR FEE0 0180H - FEE0 01F0H

31

0

Address: 0FEE0 00B0H

Value after reset: 0H