Vol. 3C 35-319

MODEL-SPECIFIC REGISTERS (MSRS)

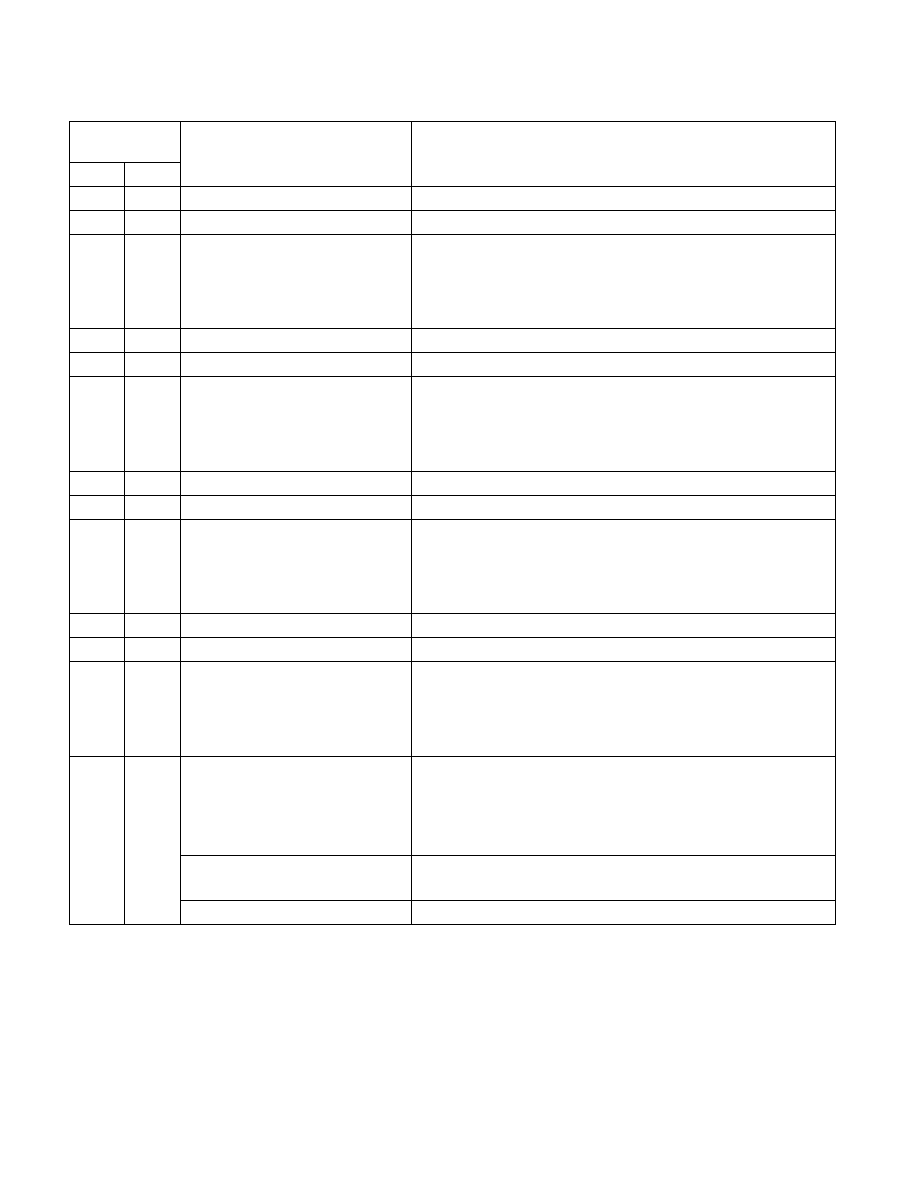

35.21 MSRS IN THE P6 FAMILY PROCESSORS

The following MSRs are defined for the P6 family processors. The MSRs in this table that are shaded are available

only in the Pentium II and Pentium III processors. Beginning with the Pentium 4 processor, some of the MSRs in this

list have been designated as тАЬarchitecturalтАЭ and have had their names changed. See Table 35-2 for a list of the

architectural MSRs.

404H

1028

IA32_MC1_CTL

See Section 15.3.2.1, тАЬIA32_MCi_CTL MSRs.тАЭ

405H

1029

IA32_MC1_STATUS

See Section 15.3.2.2, тАЬIA32_MCi_STATUS MSRS.тАЭ

406H

1030

IA32_MC1_ADDR

See Section 15.3.2.3, тАЬIA32_MCi_ADDR MSRs.тАЭ

The IA32_MC1_ADDR register is either not implemented or contains no

address if the ADDRV flag in the IA32_MC1_STATUS register is clear.

When not implemented in the processor, all reads and writes to this MSR

will cause a general-protection exception.

408H

1032

IA32_MC2_CTL

See Section 15.3.2.1, тАЬIA32_MCi_CTL MSRs.тАЭ

409H

1033

IA32_MC2_STATUS

See Chapter 15.3.2.2, тАЬIA32_MCi_STATUS MSRS.тАЭ

40AH

1034

IA32_MC2_ADDR

See Section 15.3.2.3, тАЬIA32_MCi_ADDR MSRs.тАЭ

The IA32_MC2_ADDR register is either not implemented or contains no

address if the ADDRV flag in the IA32_MC2_STATUS register is clear.

When not implemented in the processor, all reads and writes to this MSR

will cause a general-protection exception.

40CH

1036

MSR_MC4_CTL

See Section 15.3.2.1, тАЬIA32_MCi_CTL MSRs.тАЭ

40DH

1037

MSR_MC4_STATUS

See Section 15.3.2.2, тАЬIA32_MCi_STATUS MSRS.тАЭ

40EH

1038

MSR_MC4_ADDR

See Section 15.3.2.3, тАЬIA32_MCi_ADDR MSRs.тАЭ

The MSR_MC4_ADDR register is either not implemented or contains no

address if the ADDRV flag in the MSR_MC4_STATUS register is clear.

When not implemented in the processor, all reads and writes to this MSR

will cause a general-protection exception.

410H

1040

MSR_MC3_CTL

See Section 15.3.2.1, тАЬIA32_MCi_CTL MSRs.тАЭ

411H

1041

MSR_MC3_STATUS

See Section 15.3.2.2, тАЬIA32_MCi_STATUS MSRS.тАЭ

412H

1042

MSR_MC3_ADDR

See Section 15.3.2.3, тАЬIA32_MCi_ADDR MSRs.тАЭ

The MSR_MC3_ADDR register is either not implemented or contains no

address if the ADDRV flag in the MSR_MC3_STATUS register is clear.

When not implemented in the processor, all reads and writes to this MSR

will cause a general-protection exception.

600H

1536

IA32_DS_AREA

DS Save Area (R/W)

See Table 35-2.

Points to the DS buffer management area, which is used to manage the

BTS and PEBS buffers. See Section 18.12.4, тАЬDebug Store (DS)

31:0

DS Buffer Management Area

Linear address of the first byte of the DS buffer management area.

63:32

Reserved.

Table 35-45. MSRs in Pentium M Processors (Contd.)

Register

Address

Register Name

Bit Description

Hex

Dec