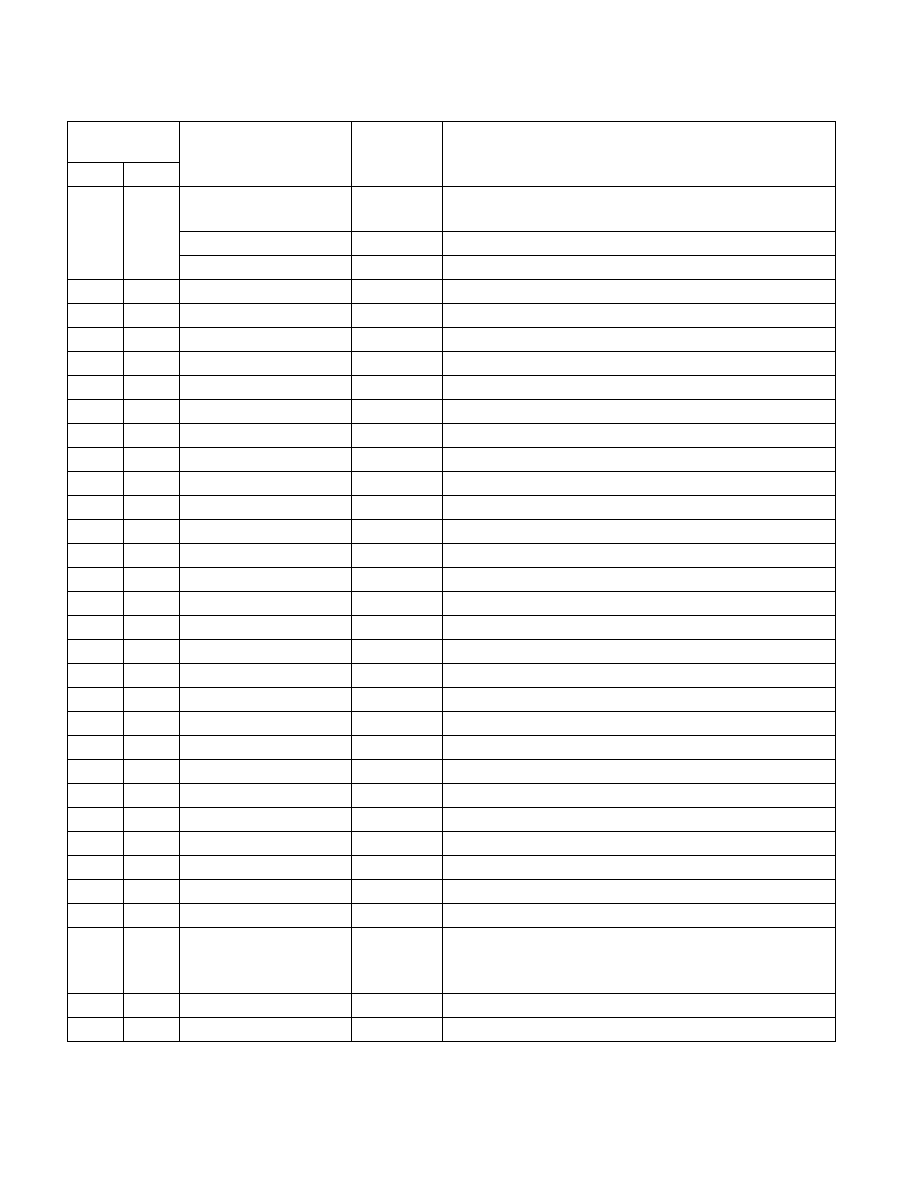

35-310 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

1E0H

480

ROB_CR_

BKUPTMPDR6

Unique

1:0

Reserved.

2

Fast String Enable bit. (Default, enabled)

200H

512

MTRRphysBase0

Unique

201H

513

MTRRphysMask0

Unique

202H

514

MTRRphysBase1

Unique

203H

515

MTRRphysMask1

Unique

204H

516

MTRRphysBase2

Unique

205H

517

MTRRphysMask2

Unique

206H

518

MTRRphysBase3

Unique

207H

519

MTRRphysMask3

Unique

208H

520

MTRRphysBase4

Unique

209H

521

MTRRphysMask4

Unique

20AH

522

MTRRphysBase5

Unique

20BH

523

MTRRphysMask5

Unique

20CH

524

MTRRphysBase6

Unique

20DH

525

MTRRphysMask6

Unique

20EH

526

MTRRphysBase7

Unique

20FH

527

MTRRphysMask7

Unique

250H

592

MTRRfix64K_00000

Unique

258H

600

MTRRfix16K_80000

Unique

259H

601

MTRRfix16K_A0000

Unique

268H

616

MTRRfix4K_C0000

Unique

269H

617

MTRRfix4K_C8000

Unique

26AH

618

MTRRfix4K_D0000

Unique

26BH

619

MTRRfix4K_D8000

Unique

26CH

620

MTRRfix4K_E0000

Unique

26DH

621

MTRRfix4K_E8000

Unique

26EH

622

MTRRfix4K_F0000

Unique

26FH

623

MTRRfix4K_F8000

Unique

2FFH

767

IA32_MTRR_DEF_TYPE

Unique

Default Memory Types (R/W)

See Table 35-2.

See Section 11.11.2.1, “IA32_MTRR_DEF_TYPE MSR.”

400H

1024

IA32_MC0_CTL

Unique

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

401H

1025

IA32_MC0_STATUS

Unique

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS.”

Table 35-44. MSRs in Intel® Core™ Solo, Intel® Core™ Duo Processors, and Dual-Core Intel® Xeon® Processor LV

Register

Address

Register Name

Shared/

Unique

Bit Description

Hex

Dec