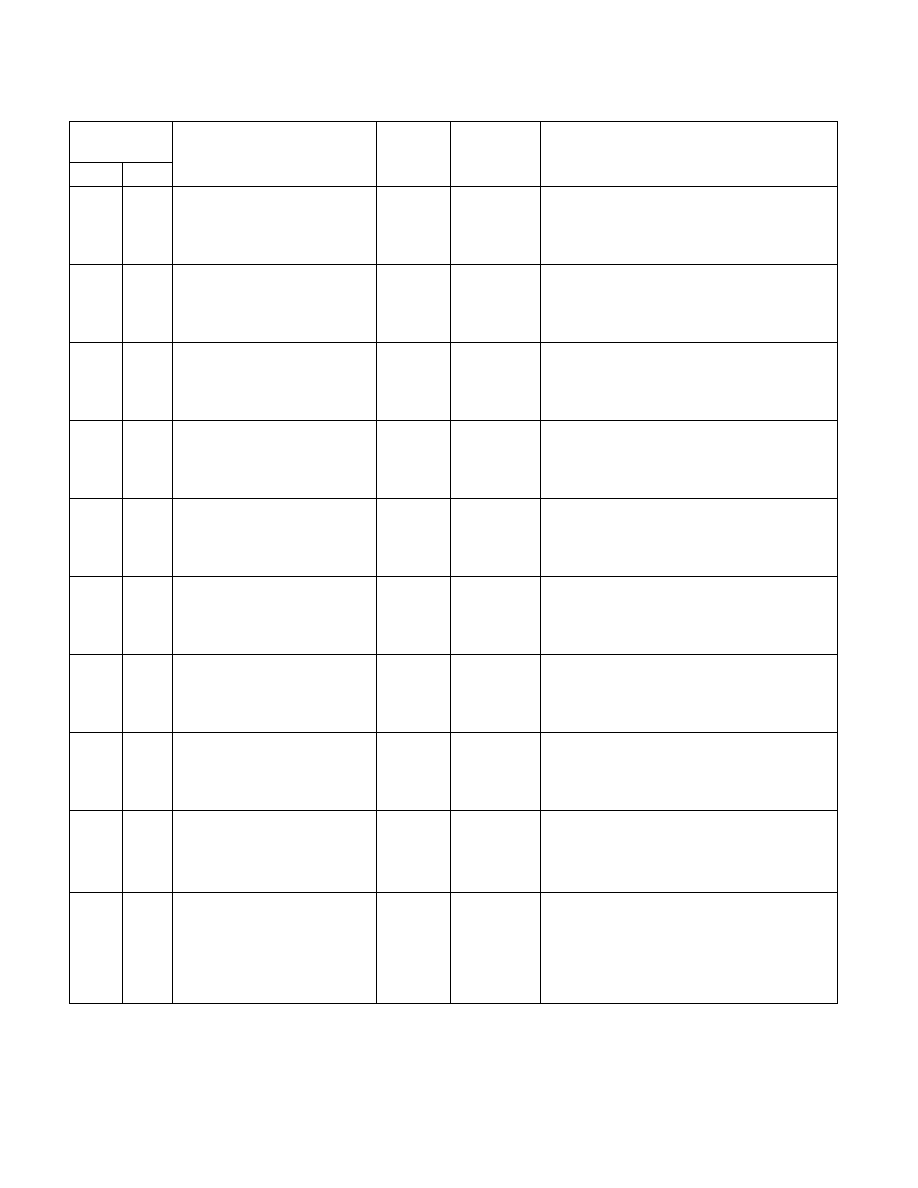

Vol. 3C 35-299

MODEL-SPECIFIC REGISTERS (MSRS)

484H 1156

IA32_VMX_ENTRY_CTLS

3, 4, 6

Unique

Capability Reporting Register of VM-entry

Controls (R/O)

See Appendix A.5, “VM-Entry Controls,” and see

485H 1157

IA32_VMX_MISC

3, 4, 6

Unique

Reporting Register of Miscellaneous VMX

Capabilities (R/O)

See Appendix A.6, “Miscellaneous Data,” and see

486H 1158

IA32_VMX_CR0_FIXED0

3, 4, 6

Unique

Capability Reporting Register of CR0 Bits Fixed

to 0 (R/O)

See Appendix A.7, “VMX-Fixed Bits in CR0,” and

487H 1159

IA32_VMX_CR0_FIXED1

3, 4, 6

Unique

Capability Reporting Register of CR0 Bits Fixed

to 1 (R/O)

See Appendix A.7, “VMX-Fixed Bits in CR0,” and

488H 1160

IA32_VMX_CR4_FIXED0

3, 4, 6

Unique

Capability Reporting Register of CR4 Bits Fixed

to 0 (R/O)

See Appendix A.8, “VMX-Fixed Bits in CR4,” and

489H 1161

IA32_VMX_CR4_FIXED1

3, 4, 6

Unique

Capability Reporting Register of CR4 Bits Fixed

to 1 (R/O)

See Appendix A.8, “VMX-Fixed Bits in CR4,” and

48AH 1162

IA32_VMX_VMCS_ENUM

3, 4, 6

Unique

Capability Reporting Register of VMCS Field

Enumeration (R/O)

See Appendix A.9, “VMCS Enumeration,” and see

48BH 1163

IA32_VMX_PROCBASED_CTLS2

3, 4, 6

Unique

Capability Reporting Register of Secondary

Processor-based VM-execution Controls (R/O)

See Appendix A.3, “VM-Execution Controls,” and

600H

1536 IA32_DS_AREA

0, 1, 2, 3,

4, 6

Unique

DS Save Area (R/W)

See Table 35-2.

See Section 18.12.4, “Debug Store (DS)

680H

1664

MSR_LASTBRANCH_0_FROM_IP

3, 4, 6

Unique

Last Branch Record 0 (R/W)

One of 16 pairs of last branch record registers on

the last branch record stack (680H-68FH). This

part of the stack contains pointers to the source

instruction for one of the last 16 branches,

exceptions, or interrupts taken by the processor.

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec