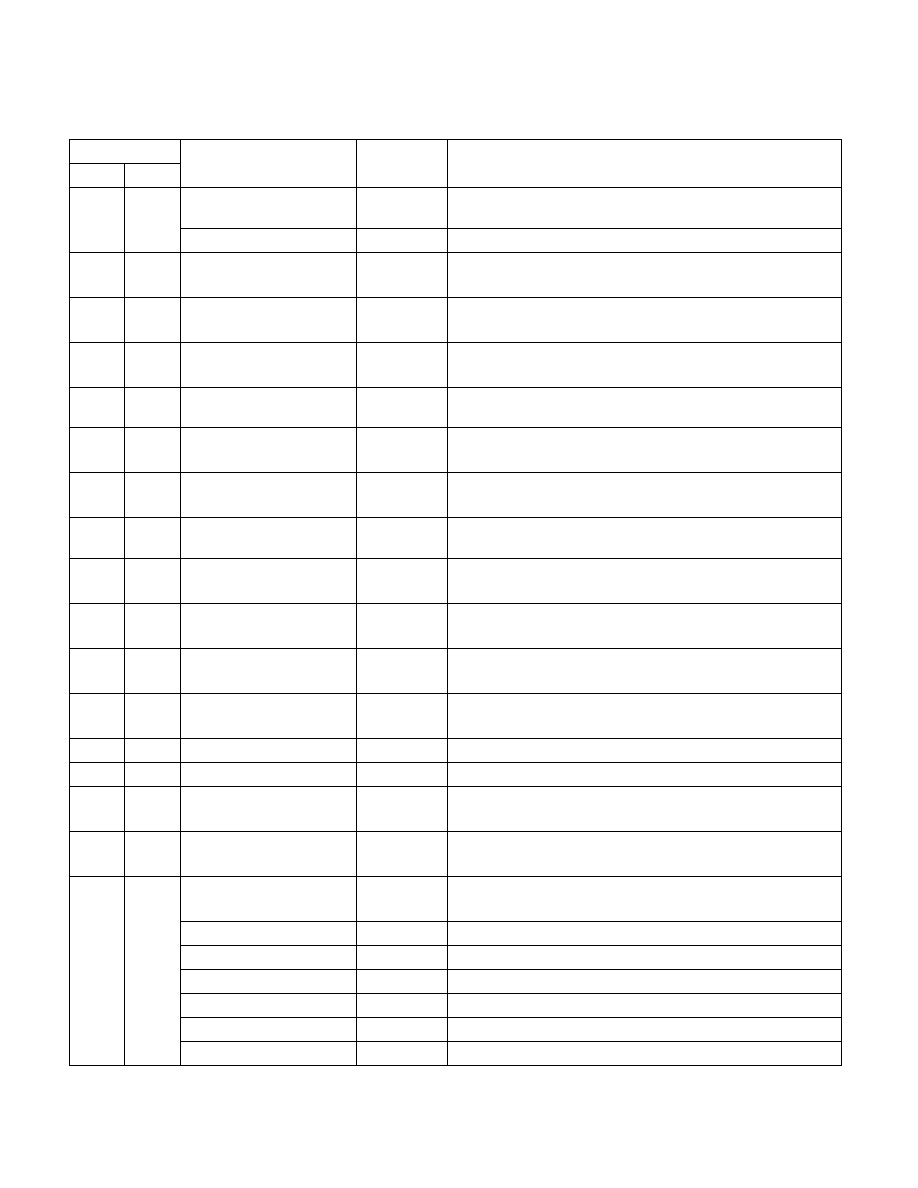

Vol. 3C 35-275

MODEL-SPECIFIC REGISTERS (MSRS)

60DH

1549

MSR_PKG_C2_RESIDENCY

Package

Note: C-state values are processor specific C-state code names,

unrelated to MWAIT extension C-state parameters or ACPI C-States.

63:0

Package C2 Residency Counter. (R/O)

610H

1552

MSR_PKG_POWER_LIMIT

Package

PKG RAPL Power Limit Control (R/W)

See Section 14.9.3, “Package RAPL Domain.”

611H

1553

MSR_PKG_ENERGY_STATUS Package

PKG Energy Status (R/O)

See Section 14.9.3, “Package RAPL Domain.”

613H

1555

MSR_PKG_PERF_STATUS

Package

PKG Perf Status (R/O)

See Section 14.9.3, “Package RAPL Domain.”

614H

1556

MSR_PKG_POWER_INFO

Package

PKG RAPL Parameters (R/W) See Section 14.9.3, “Package RAPL

618H

1560

MSR_DRAM_POWER_LIMIT

Package

DRAM RAPL Power Limit Control (R/W)

See Section 14.9.5, “DRAM RAPL Domain.”

619H

1561

MSR_DRAM_ENERGY_

STATUS

Package

DRAM Energy Status (R/O)

See Section 14.9.5, “DRAM RAPL Domain.”

61BH

1563

MSR_DRAM_PERF_STATUS

Package

DRAM Performance Throttling Status (R/O) See Section 14.9.5,

61CH

1564

MSR_DRAM_POWER_INFO

Package

DRAM RAPL Parameters (R/W)

See Section 14.9.5, “DRAM RAPL Domain.”

638H

1592

MSR_PP0_POWER_LIMIT

Package

PP0 RAPL Power Limit Control (R/W)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

639H

1593

MSR_PP0_ENERGY_STATUS Package

PP0 Energy Status (R/O)

See Section 14.9.4, “PP0/PP1 RAPL Domains.”

648H

1608

MSR_CONFIG_TDP_

NOMINAL

Package

Base TDP Ratio (R/O)

See Table 35-23

649H

1609

MSR_CONFIG_TDP_LEVEL1

Package

ConfigTDP Level 1 ratio and power level (R/O). See Table 35-23

64AH

1610

MSR_CONFIG_TDP_LEVEL2

Package

ConfigTDP Level 2 ratio and power level (R/O). See Table 35-23

64BH

1611

MSR_CONFIG_TDP_

CONTROL

Package

ConfigTDP Control (R/W)

See Table 35-23

64CH

1612

MSR_TURBO_ACTIVATION_

RATIO

Package

ConfigTDP Control (R/W)

See Table 35-23

690H

1680

MSR_CORE_PERF_LIMIT_RE

ASONS

Package

Indicator of Frequency Clipping in Processor Cores (R/W)

(frequency refers to processor core frequency)

0

PROCHOT Status (R0)

1

Thermal Status (R0)

5:2

Reserved.

6

VR Therm Alert Status (R0)

7

Reserved.

8

Electrical Design Point Status (R0)

Table 35-40. Selected MSRs Supported by Intel® Xeon Phi™ Processors with DisplayFamily_DisplayModel Signature

06_57H

Address

Register Name

Scope

Bit Description

Hex

Dec