Vol. 3B 14-33

POWER AND THERMAL MANAGEMENT

The presence of the optional MSR interfaces (the three right-most columns of Table 14-4) may be model-specific.

See Chapter 35 for detail.

14.9.3

Package RAPL Domain

The MSR interfaces defined for the package RAPL domain are:

•

MSR_PKG_POWER_LIMIT allows software to set power limits for the package and measurement attributes

associated with each limit,

•

MSR_PKG_ENERGY_STATUS reports measured actual energy usage,

•

MSR_PKG_POWER_INFO reports the package power range information for RAPL usage.

MSR_PKG_PERF_STATUS can report the performance impact of power limiting, but its availability may be model-

specific.

MSR_PKG_POWER_LIMIT allows a software agent to define power limitation for the package domain. Power limita-

tion is defined in terms of average power usage (Watts) over a time window specified in MSR_PKG_POWER_LIMIT.

Two power limits can be specified, corresponding to time windows of different sizes. Each power limit provides

independent clamping control that would permit the processor cores to go below OS-requested state to meet the

power limits. A lock mechanism allow the software agent to enforce power limit settings. Once the lock bit is set,

the power limit settings are static and un-modifiable until next RESET.

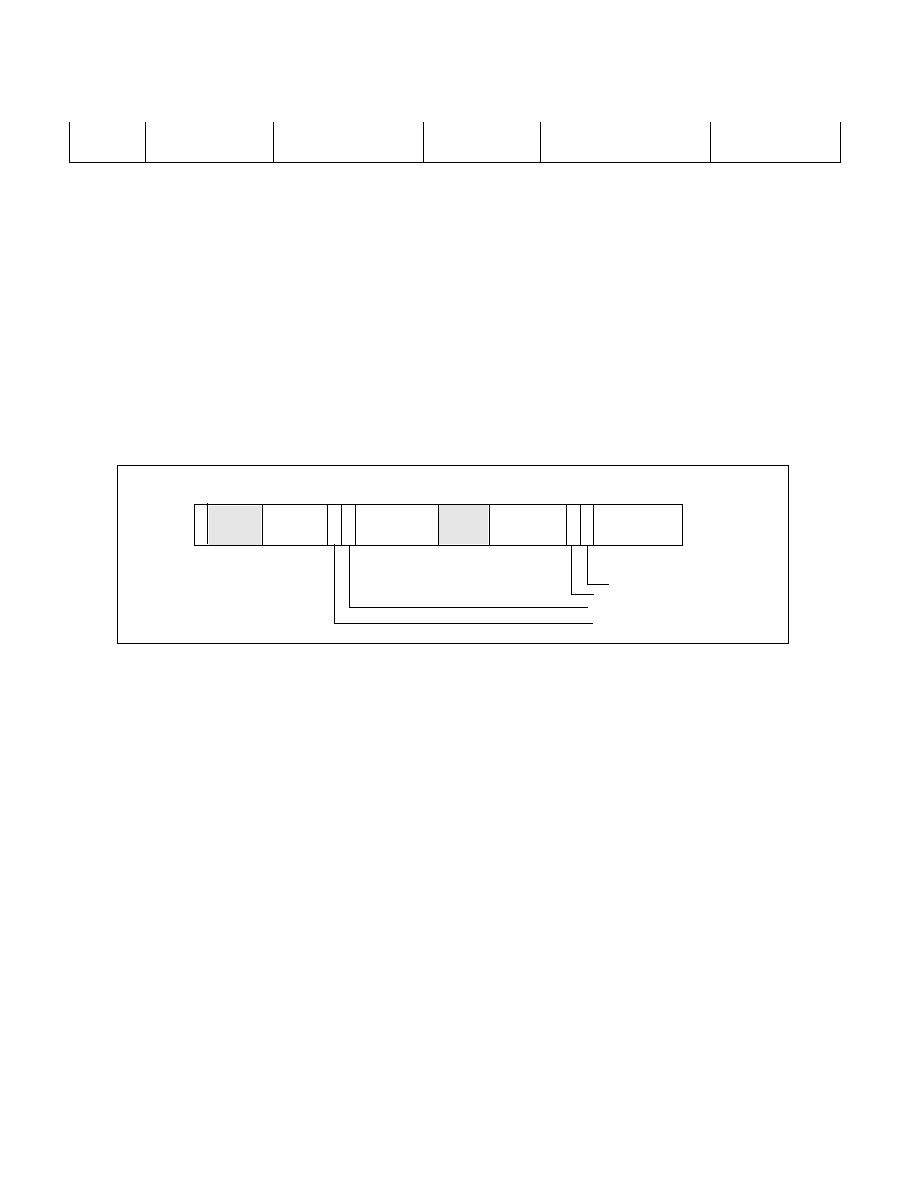

The bit fields of MSR_PKG_POWER_LIMIT (Figure 14-32) are:

•

Package Power Limit #1(bits 14:0): Sets the average power usage limit of the package domain corre-

sponding to time window # 1. The unit of this field is specified by the “Power Units” field of

MSR_RAPL_POWER_UNIT.

•

Enable Power Limit #1(bit 15): 0 = disabled; 1 = enabled.

•

Package Clamping Limitation #1 (bit 16): Allow going below OS-requested P/T state setting during time

window specified by bits 23:17.

•

Time Window for Power Limit #1 (bits 23:17): Indicates the time window for power limit #1

Time limit = 2^Y * (1.0 + Z/4.0) * Time_Unit

Here “Y” is the unsigned integer value represented. by bits 21:17, “Z” is an unsigned integer represented by

bits 23:22. “Time_Unit” is specified by the “Time Units” field of MSR_RAPL_POWER_UNIT.

PP1

MSR_PP1_POWER_

LIMIT

MSR_PP1_ENERGY_STA

TUS

MSR_PP1_POLICY RESERVED

RESERVED

Figure 14-32. MSR_PKG_POWER_LIMIT Register

Table 14-4. RAPL MSR Interfaces and RAPL Domains

63

Enable limit #1

Pkg clamping limit #1

Enable limit #2

Pkg clamping limit #2

31

24 23

15

0

Pkg Power Limit #1

48 47

32

62

56 55

49

46

14

L

O

C

Pkg Power Limit #2

16

17

K

Time window

Power Limit #2

Time window

Power Limit #1