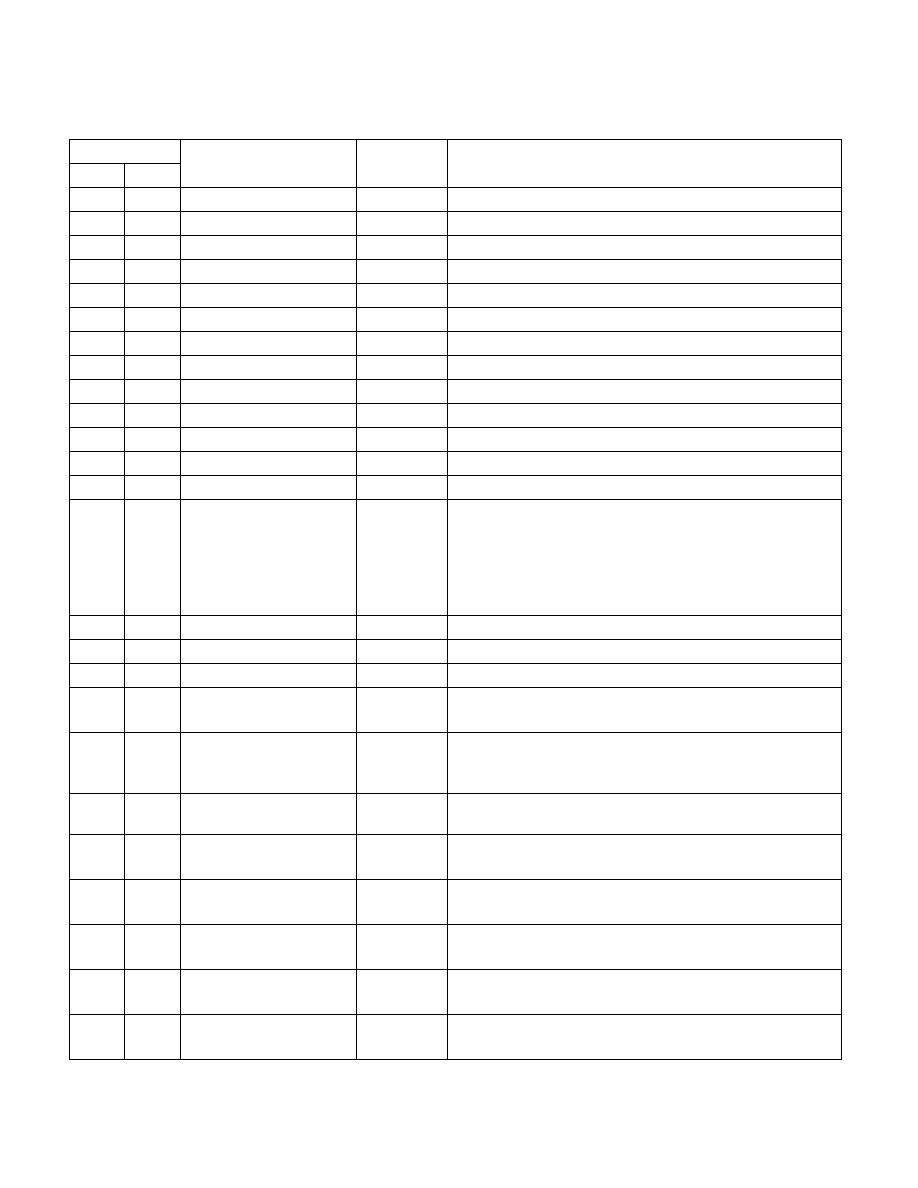

Vol. 3C 35-273

MODEL-SPECIFIC REGISTERS (MSRS)

400H

1024

IA32_MC0_CTL

Core

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

401H

1025

IA32_MC0_STATUS

Core

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS.”

402H

1026

IA32_MC0_ADDR

Core

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

404H

1028

IA32_MC1_CTL

Core

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

405H

1029

IA32_MC1_STATUS

Core

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS.”

408H

1032

IA32_MC2_CTL

Core

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

409H

1033

IA32_MC2_STATUS

Core

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS.”

40AH

1034

IA32_MC2_ADDR

Core

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

40CH

1036

IA32_MC3_CTL

Core

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

40DH

1037

IA32_MC3_STATUS

Core

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS.”

40EH

1038

IA32_MC3_ADDR

Core

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

410H

1040

IA32_MC4_CTL

Core

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

411H

1041

IA32_MC4_STATUS

Core

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS.”

412H

1042

IA32_MC4_ADDR

Core

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

The MSR_MC4_ADDR register is either not implemented or

contains no address if the ADDRV flag in the MSR_MC4_STATUS

register is clear.

When not implemented in the processor, all reads and writes to this

MSR will cause a general-protection exception.

414H

1044

IA32_MC5_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.”

415H

1045

IA32_MC5_STATUS

Package

See Section 15.3.2.2, “IA32_MCi_STATUS MSRS.”

416H

1046

IA32_MC5_ADDR

Package

See Section 15.3.2.3, “IA32_MCi_ADDR MSRs.”

480H

1152

IA32_VMX_BASIC

Core

Reporting Register of Basic VMX Capabilities (R/O)

See Table 35-2.

481H

1153

IA32_VMX_PINBASED_

CTLS

Core

Capability Reporting Register of Pin-based VM-execution

Controls (R/O)

See Table 35-2.

482H

1154

IA32_VMX_PROCBASED_

CTLS

Core

Capability Reporting Register of Primary Processor-based

VM-execution Controls (R/O)

483H

1155

IA32_VMX_EXIT_CTLS

Core

Capability Reporting Register of VM-exit Controls (R/O)

See Table 35-2.

484H

1156

IA32_VMX_ENTRY_CTLS

Core

Capability Reporting Register of VM-entry Controls (R/O)

See Table 35-2.

485H

1157

IA32_VMX_MISC

Core

Reporting Register of Miscellaneous VMX Capabilities (R/O)

See Table 35-2.

486H

1158

IA32_VMX_CR0_FIXED0

Core

Capability Reporting Register of CR0 Bits Fixed to 0 (R/O)

See Table 35-2.

487H

1159

IA32_VMX_CR0_FIXED1

Core

Capability Reporting Register of CR0 Bits Fixed to 1 (R/O)

See Table 35-2.

Table 35-40. Selected MSRs Supported by Intel® Xeon Phi™ Processors with DisplayFamily_DisplayModel Signature

06_57H

Address

Register Name

Scope

Bit Description

Hex

Dec