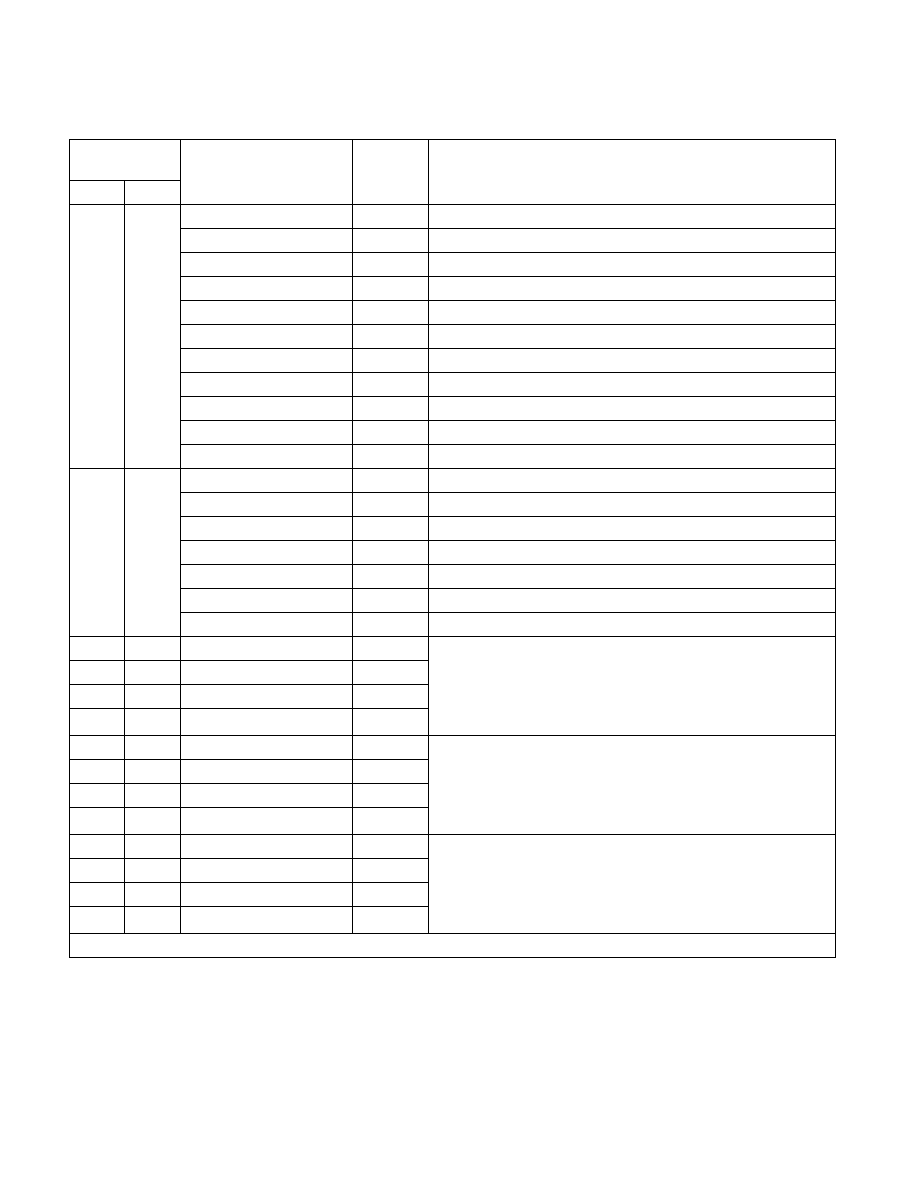

Vol. 3C 35-185

MODEL-SPECIFIC REGISTERS (MSRS)

3F1H

1009

MSR_PEBS_ENABLE

Thread

See Section 18.7.1.1, “Precise Event Based Sampling (PEBS).”

0

Enable PEBS on IA32_PMC0. (R/W)

1

Enable PEBS on IA32_PMC1. (R/W)

2

Enable PEBS on IA32_PMC2. (R/W)

3

Enable PEBS on IA32_PMC3. (R/W)

31:4

Reserved.

32

Enable Load Latency on IA32_PMC0. (R/W)

33

Enable Load Latency on IA32_PMC1. (R/W)

34

Enable Load Latency on IA32_PMC2. (R/W)

35

Enable Load Latency on IA32_PMC3. (R/W)

63:36

Reserved.

41BH

1051

IA32_MC6_MISC

Package

Misc MAC information of Integrated I/O. (R/O) see Section 15.3.2.4

5:0

Recoverable Address LSB

8:6

Address Mode

15:9

Reserved

31:16

PCI Express Requestor ID

39:32

PCI Express Segment Number

63:32

Reserved

474H

1140

IA32_MC29_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC29 reports MC error from a specific CBo (core broadcast) and

its corresponding slice of L3.

475H

1141

IA32_MC29_STATUS

Package

476H

1142

IA32_MC29_ADDR

Package

477H

1143

IA32_MC29_MISC

Package

478H

1144

IA32_MC30_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC30 reports MC error from a specific CBo (core broadcast) and

its corresponding slice of L3.

479H

1145

IA32_MC30_STATUS

Package

47AH

1146

IA32_MC30_ADDR

Package

47BH

1147

IA32_MC30_MISC

Package

47CH

1148

IA32_MC31_CTL

Package

See Section 15.3.2.1, “IA32_MCi_CTL MSRs.” through Section

15.3.2.4, “IA32_MCi_MISC MSRs.”.

Bank MC31 reports MC error from a specific CBo (core broadcast) and

its corresponding slice of L3.

47DH

1149

IA32_MC31_STATUS

Package

47EH

1150

IA32_MC31_ADDR

Package

47FH

1147

IA32_MC31_MISC

Package

See Table 35-18, Table 35-24 for other MSR definitions applicable to Intel Xeon processor E7 v2 with CPUID signature 06_3AH.

NOTES:

1. An override configuration lower than the factory-set configuration is always supported. An override configuration higher than the

factory-set configuration is dependent on features specific to the processor and the platform.

Table 35-25. Additional MSRs Supported by Intel® Xeon® Processor E7 v2 Family with DisplayFamily_DisplayModel

Signature 06_3EH

Register

Address

Register Name

Scope

Bit Description

Hex

Dec