Vol. 3C 35-167

MODEL-SPECIFIC REGISTERS (MSRS)

47:40

Package

Maximum Ratio Limit for 6C

Maximum turbo ratio limit of 6 core active.

55:48

Package

Maximum Ratio Limit for 7C

Maximum turbo ratio limit of 7 core active.

63:56

Package

Maximum Ratio Limit for 8C

Maximum turbo ratio limit of 8 core active.

285H

645

IA32_MC5_CTL2

Package

286H

646

IA32_MC6_CTL2

Package

287H

647

IA32_MC7_CTL2

Package

288H

648

IA32_MC8_CTL2

Package

289H

649

IA32_MC9_CTL2

Package

28AH

650

IA32_MC10_CTL2

Package

See Table 35-2.

28BH

651

IA32_MC11_CTL2

Package

See Table 35-2.

28CH

652

IA32_MC12_CTL2

Package

See Table 35-2.

28DH

653

IA32_MC13_CTL2

Package

See Table 35-2.

28EH

654

IA32_MC14_CTL2

Package

See Table 35-2.

28FH

655

IA32_MC15_CTL2

Package

See Table 35-2.

290H

656

IA32_MC16_CTL2

Package

See Table 35-2.

291H

657

IA32_MC17_CTL2

Package

See Table 35-2.

292H

658

IA32_MC18_CTL2

Package

See Table 35-2.

293H

659

IA32_MC19_CTL2

Package

See Table 35-2.

39CH

924

MSR_PEBS_NUM_ALT

Package

0

ENABLE_PEBS_NUM_ALT (RW)

Write 1 to enable alternate PEBS counting logic for specific events

requiring additional configuration, see Table 19-9

63:1

Reserved (must be zero).

414H

1044

IA32_MC5_CTL

Package

See Section 15.3.2.1, ÔÇťIA32_MCi_CTL MSRs.ÔÇŁ

415H

1045

IA32_MC5_STATUS

Package

See Section 15.3.2.2, ÔÇťIA32_MCi_STATUS MSRS,ÔÇŁ and Chapter 16.

416H

1046

IA32_MC5_ADDR

Package

See Section 15.3.2.3, ÔÇťIA32_MCi_ADDR MSRs.ÔÇŁ

417H

1047

IA32_MC5_MISC

Package

See Section 15.3.2.4, ÔÇťIA32_MCi_MISC MSRs.ÔÇŁ

418H

1048

IA32_MC6_CTL

Package

See Section 15.3.2.1, ÔÇťIA32_MCi_CTL MSRs.ÔÇŁ

419H

1049

IA32_MC6_STATUS

Package

See Section 15.3.2.2, ÔÇťIA32_MCi_STATUS MSRS,ÔÇŁ and Chapter 16.

41AH

1050

IA32_MC6_ADDR

Package

See Section 15.3.2.3, ÔÇťIA32_MCi_ADDR MSRs.ÔÇŁ

41BH

1051

IA32_MC6_MISC

Package

See Section 15.3.2.4, ÔÇťIA32_MCi_MISC MSRs.ÔÇŁ

41CH

1052

IA32_MC7_CTL

Package

See Section 15.3.2.1, ÔÇťIA32_MCi_CTL MSRs.ÔÇŁ

41DH

1053

IA32_MC7_STATUS

Package

See Section 15.3.2.2, ÔÇťIA32_MCi_STATUS MSRS,ÔÇŁ and Chapter 16.

41EH

1054

IA32_MC7_ADDR

Package

See Section 15.3.2.3, ÔÇťIA32_MCi_ADDR MSRs.ÔÇŁ

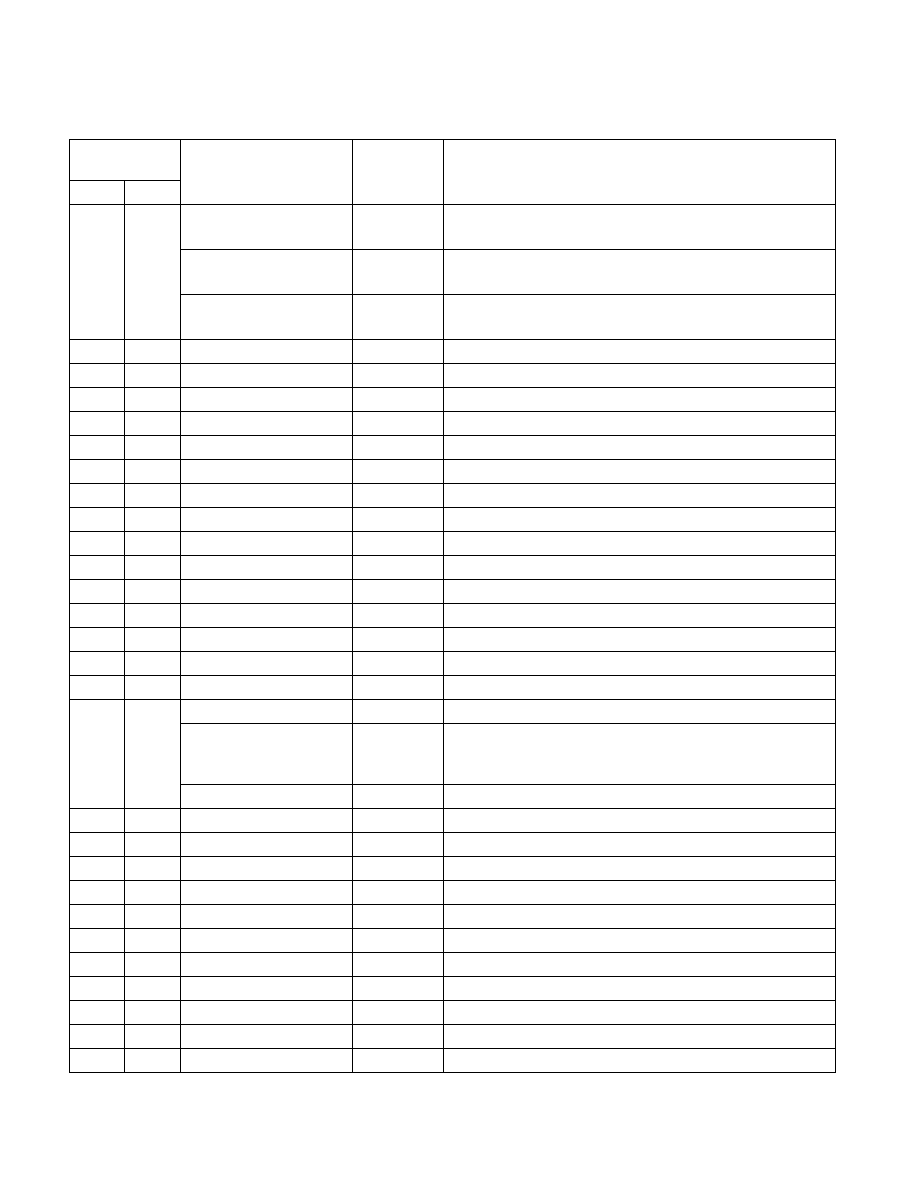

Table 35-21. Selected MSRs Supported by Intel® Xeon® Processors E5 Family (based on Sandy Bridge

microarchitecture) (Contd.)

Register

Address

Register Name

Scope

Bit Description

Hex

Dec