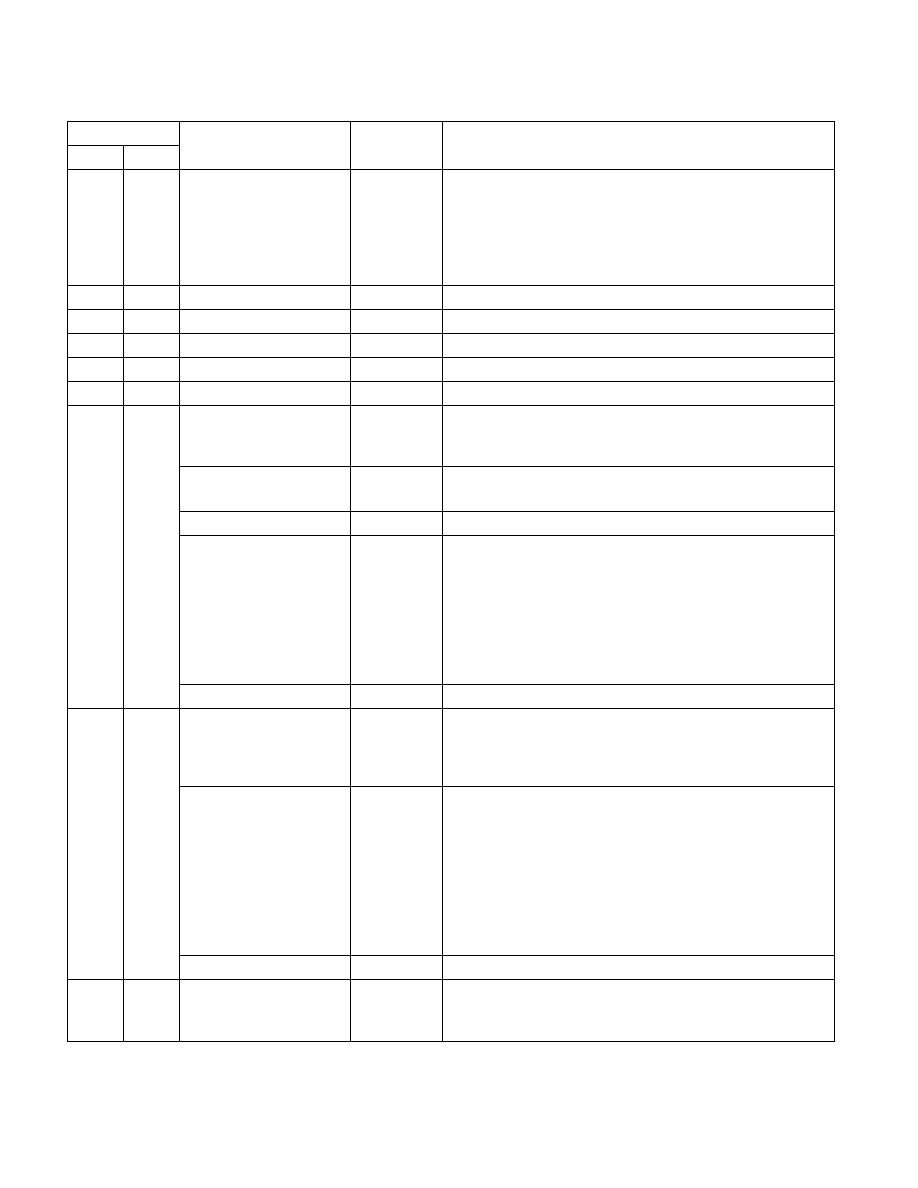

35-94 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

406H

1030

IA32_MC1_ADDR

Module

See Section 15.3.2.3, ŌĆ£IA32_MCi_ADDR MSRs.ŌĆØ

The IA32_MC2_ADDR register is either not implemented or

contains no address if the ADDRV flag in the IA32_MC2_STATUS

register is clear.

When not implemented in the processor, all reads and writes to this

MSR will cause a general-protection exception.

418H

1048

IA32_MC6_CTL

Package

See Section 15.3.2.1, ŌĆ£IA32_MCi_CTL MSRs.ŌĆØ

419H

1049

IA32_MC6_STATUS

Package

See Section 15.3.2.2, ŌĆ£IA32_MCi_STATUS MSRS,ŌĆØ and Chapter 16.

41AH

1050

IA32_MC6_ADDR

Package

See Section 15.3.2.3, ŌĆ£IA32_MCi_ADDR MSRs.ŌĆØ

4C3H

1219

IA32_A_PMC2

Core

4C4H

1220

IA32_A_PMC3

Core

4E0H

1248

MSR_SMM_FEATURE_CONT

ROL

Package

Enhanced SMM Feature Control (SMM-RW)

Reports SMM capability Enhancement. Accessible only while in

SMM.

0

Lock (SMM-RWO)

When set to ŌĆś1ŌĆÖ locks this register from further changes

1

Reserved

2

SMM_Code_Chk_En (SMM-RW)

This control bit is available only if MSR_SMM_MCA_CAP[58] == 1.

When set to ŌĆś0ŌĆÖ (default) none of the logical processors are

prevented from executing SMM code outside the ranges defined by

the SMRR.

When set to ŌĆś1ŌĆÖ any logical processor in the package that attempts

to execute SMM code not within the ranges defined by the SMRR

will assert an unrecoverable MCE.

63:3

Reserved

4E2H

1250

MSR_SMM_DELAYED

Package

SMM Delayed (SMM-RO)

Reports the interruptible state of all logical processors in the

package. Available only while in SMM and

MSR_SMM_MCA_CAP[LONG_FLOW_INDICATION] == 1.

N-1:0

LOG_PROC_STATE (SMM-RO)

Each bit represents a processor core of its state in a long flow of

internal operation which delays servicing an interrupt. The

corresponding bit will be set at the start of long events such as:

Microcode Update Load, C6, WBINVD, Ratio Change, Throttle.

The bit is automatically cleared at the end of each long event. The

reset value of this field is 0.

Only bit positions below N = CPUID.(EAX=0BH,

ECX=PKG_LVL):EBX[15:0] can be updated.

63:N

Reserved

4E3H

1251

MSR_SMM_BLOCKED

Package

SMM Blocked (SMM-RO)

Reports the blocked state of all logical processors in the package.

Available only while in SMM.

Table 35-12. MSRs in Next Generation Intel Atom Processors Based on the Goldmont Microarchitecture (Contd.)

Address

Register Name

Scope

Bit Description

Hex

Dec