Vol. 3C 35-83

MODEL-SPECIFIC REGISTERS (MSRS)

35.4.2 MSRs In Intel Atom Processors Based on Airmont Microarchitecture

Intel Atom processor X7-Z8000 and X5-Z8000 series are based on the Airmont microarchitecture. These proces-

sors support MSRs listed in Table 35-6, Table 35-7, Table 35-8, and Table 35-11. These processors have a CPUID

signature with DisplayFamily_DisplayModel including 06_4CH; see Table 35-1.

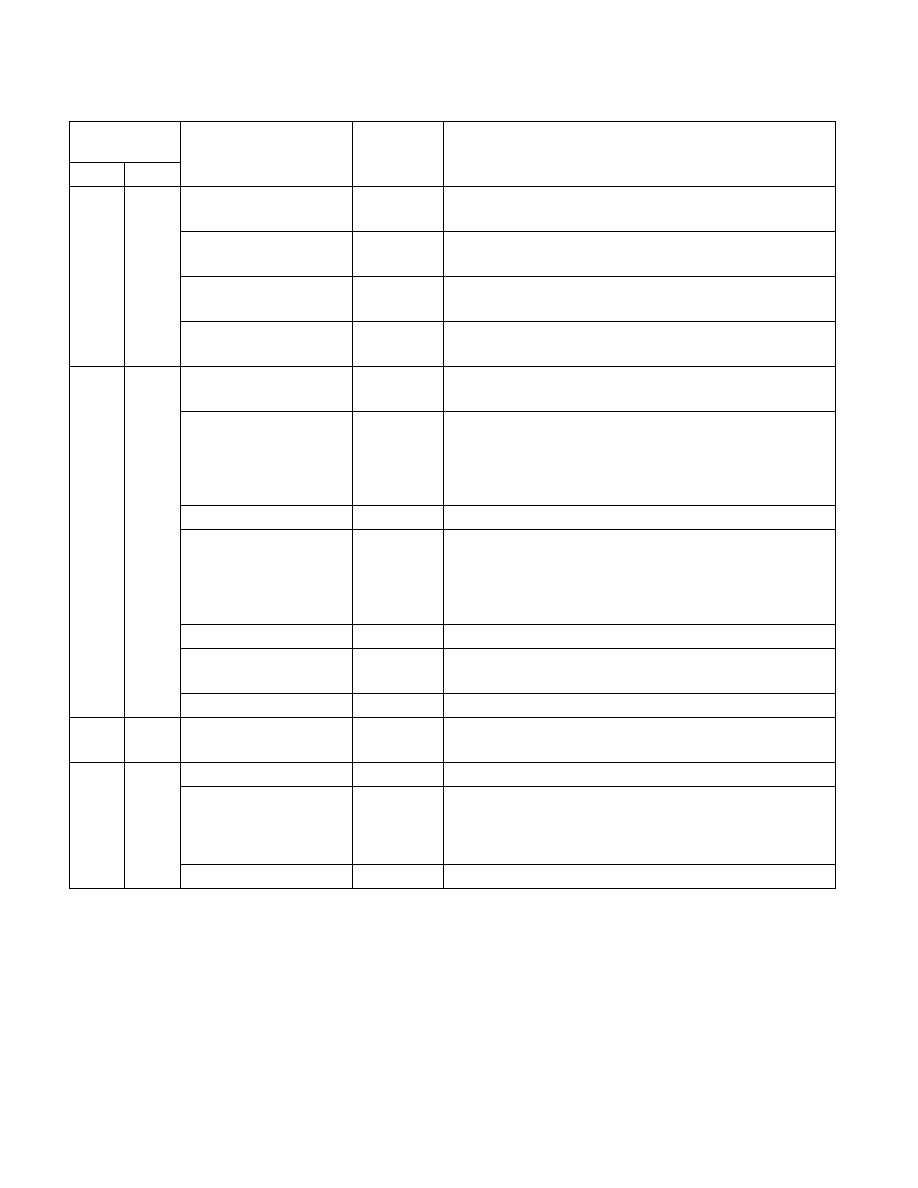

39:32

Package

Maximum Ratio Limit for 5C

Maximum turbo ratio limit of 5 core active.

47:40

Package

Maximum Ratio Limit for 6C

Maximum turbo ratio limit of 6 core active.

55:48

Package

Maximum Ratio Limit for 7C

Maximum turbo ratio limit of 7 core active.

63:56

Package

Maximum Ratio Limit for 8C

Maximum turbo ratio limit of 8 core active.

606H

1542

MSR_RAPL_POWER_UNIT

Package

Unit Multipliers used in RAPL Interfaces (R/O)

See Section 14.9.1, “RAPL Interfaces.”

3:0

Power Units.

Power related information (in milliWatts) is based on the multiplier,

2^PU; where PU is an unsigned integer represented by bits 3:0.

Default value is 0101b, indicating power unit is in 32 milliWatts

increment.

7:4

Reserved

12:8

Energy Status Units.

Energy related information (in microJoules) is based on the

multiplier, 2^ESU; where ESU is an unsigned integer represented

by bits 12:8. Default value is 00101b, indicating energy unit is in

32 microJoules increment.

15:13

Reserved

19:16

Time Unit.

The value is 0000b, indicating time unit is in one second.

63:20

Reserved

610H

1552

MSR_PKG_POWER_LIMIT

Package

PKG RAPL Power Limit Control (R/W)

See Section 14.9.3, “Package RAPL Domain.”

66EH

1646

MSR_PKG_POWER_INFO

Package

PKG RAPL Parameter (R/0)

14:0

Thermal Spec Power. (R/0)

The unsigned integer value is the equivalent of thermal

specification power of the package domain. The unit of this field is

specified by the “Power Units” field of MSR_RAPL_POWER_UNIT

63:15

Reserved

Table 35-10. Specific MSRs Supported by Intel® Atom™ Processor C2000 Series (Contd.)with CPUID Signature

Register

Address

Register Name

Scope

Bit Description

Hex

Dec