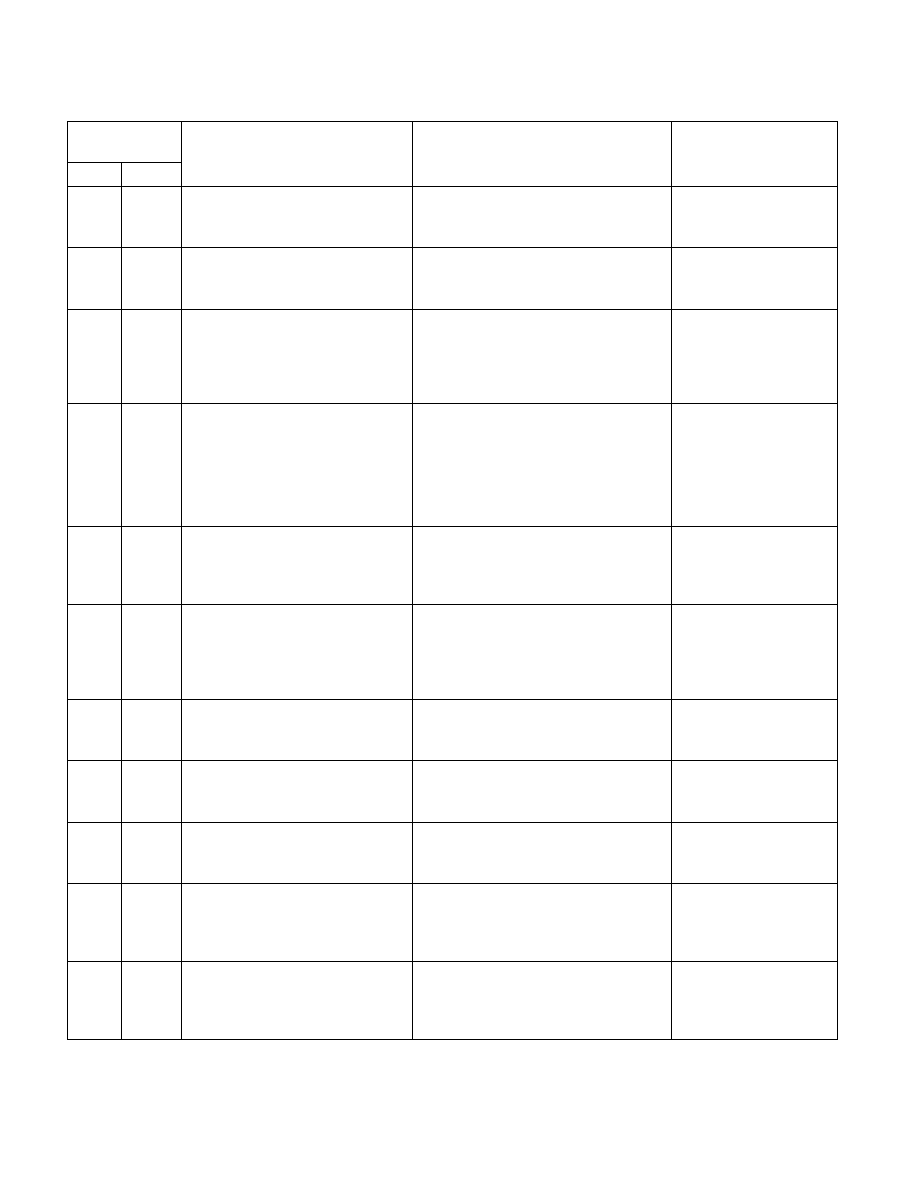

35-30 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

489H

1161

IA32_VMX_CR4_FIXED1

Capability Reporting Register of CR4 Bits

Fixed to 1 (R/O)

See Appendix A.8, “VMX-Fixed Bits in CR4.”

If CPUID.01H:ECX.[5] = 1

48AH

1162

IA32_VMX_VMCS_ENUM

Capability Reporting Register of VMCS

Field Enumeration (R/O)

See Appendix A.9, “VMCS Enumeration.”

If CPUID.01H:ECX.[5] = 1

48BH

1163

IA32_VMX_PROCBASED_CTLS2

Capability Reporting Register of

Secondary Processor-based

VM-execution Controls (R/O)

See Appendix A.3.3, “Secondary Processor-

If ( CPUID.01H:ECX.[5] &&

IA32_VMX_PROCBASED_C

TLS[63])

48CH

1164

IA32_VMX_EPT_VPID_CAP

Capability Reporting Register of EPT and

VPID (R/O)

See Appendix A.10, “VPID and EPT

If ( CPUID.01H:ECX.[5] &&

IA32_VMX_PROCBASED_C

TLS[63] && (

IA32_VMX_PROCBASED_C

TLS2[33] ||

IA32_VMX_PROCBASED_C

TLS2[37]) )

48DH

1165

IA32_VMX_TRUE_PINBASED_CTLS

Capability Reporting Register of Pin-

based VM-execution Flex Controls (R/O)

See Appendix A.3.1, “Pin-Based VM-

If ( CPUID.01H:ECX.[5] = 1

&& IA32_VMX_BASIC[55] )

48EH

1166

IA32_VMX_TRUE_PROCBASED_CTLS

Capability Reporting Register of Primary

Processor-based VM-execution Flex

Controls (R/O)

See Appendix A.3.2, “Primary Processor-

If( CPUID.01H:ECX.[5] = 1

&& IA32_VMX_BASIC[55] )

48FH

1167

IA32_VMX_TRUE_EXIT_CTLS

Capability Reporting Register of VM-exit

Flex Controls (R/O)

See Appendix A.4, “VM-Exit Controls.”

If( CPUID.01H:ECX.[5] = 1

&& IA32_VMX_BASIC[55] )

490H

1168

IA32_VMX_TRUE_ENTRY_CTLS

Capability Reporting Register of VM-

entry Flex Controls (R/O)

See Appendix A.5, “VM-Entry Controls.”

If( CPUID.01H:ECX.[5] = 1

&& IA32_VMX_BASIC[55] )

491H

1169

IA32_VMX_VMFUNC

Capability Reporting Register of VM-

function Controls (R/O)

If( CPUID.01H:ECX.[5] = 1

&& IA32_VMX_BASIC[55] )

4C1H

1217

IA32_A_PMC0

Full Width Writable IA32_PMC0 Alias (R/W) (If CPUID.0AH: EAX[15:8] >

0) &&

IA32_PERF_CAPABILITIES[

13] = 1

4C2H

1218

IA32_A_PMC1

Full Width Writable IA32_PMC1 Alias (R/W) (If CPUID.0AH: EAX[15:8] >

1) &&

IA32_PERF_CAPABILITIES[

13] = 1

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal