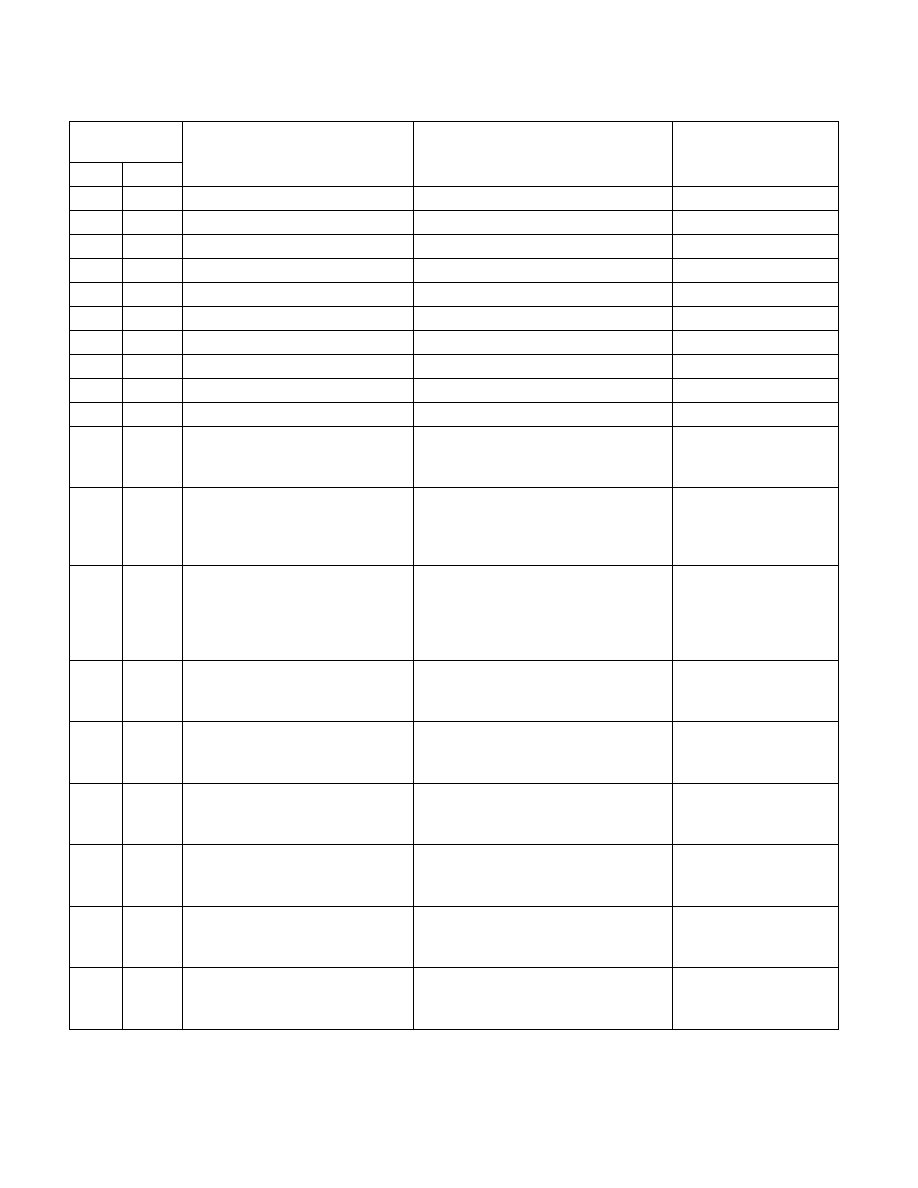

Vol. 3C 35-29

MODEL-SPECIFIC REGISTERS (MSRS)

46AH

IA32_MC26_ADDR

1

MC26_ADDR

If IA32_MCG_CAP.CNT >26

46BH

IA32_MC26_MISC

MC26_MISC

If IA32_MCG_CAP.CNT >26

46CH

IA32_MC27_CTL

MC27_CTL

If IA32_MCG_CAP.CNT >27

46DH

IA32_MC27_STATUS

MC27_STATUS

If IA32_MCG_CAP.CNT >27

46EH

IA32_MC27_ADDR

1

MC27_ADDR

If IA32_MCG_CAP.CNT >27

46FH

IA32_MC27_MISC

MC27_MISC

If IA32_MCG_CAP.CNT >27

470H

IA32_MC28_CTL

MC28_CTL

If IA32_MCG_CAP.CNT >28

471H

IA32_MC28_STATUS

MC28_STATUS

If IA32_MCG_CAP.CNT >28

472H

IA32_MC28_ADDR

1

MC28_ADDR

If IA32_MCG_CAP.CNT >28

473H

IA32_MC28_MISC

MC28_MISC

If IA32_MCG_CAP.CNT >28

480H

1152

IA32_VMX_BASIC

Reporting Register of Basic VMX

Capabilities (R/O)

See Appendix A.1, “Basic VMX Information.”

If CPUID.01H:ECX.[5] = 1

481H

1153

IA32_VMX_PINBASED_CTLS

Capability Reporting Register of Pin-

based VM-execution Controls (R/O)

See Appendix A.3.1, “Pin-Based VM-

If CPUID.01H:ECX.[5] = 1

482H

1154

IA32_VMX_PROCBASED_CTLS

Capability Reporting Register of Primary

Processor-based VM-execution Controls

(R/O)

See Appendix A.3.2, “Primary Processor-

If CPUID.01H:ECX.[5] = 1

483H

1155

IA32_VMX_EXIT_CTLS

Capability Reporting Register of VM-exit

Controls (R/O)

See Appendix A.4, “VM-Exit Controls.”

If CPUID.01H:ECX.[5] = 1

484H

1156

IA32_VMX_ENTRY_CTLS

Capability Reporting Register of VM-

entry Controls (R/O)

See Appendix A.5, “VM-Entry Controls.”

If CPUID.01H:ECX.[5] = 1

485H

1157

IA32_VMX_MISC

Reporting Register of Miscellaneous

VMX Capabilities (R/O)

See Appendix A.6, “Miscellaneous Data.”

If CPUID.01H:ECX.[5] = 1

486H

1158

IA32_VMX_CR0_FIXED0

Capability Reporting Register of CR0 Bits

Fixed to 0 (R/O)

See Appendix A.7, “VMX-Fixed Bits in CR0.”

If CPUID.01H:ECX.[5] = 1

487H

1159

IA32_VMX_CR0_FIXED1

Capability Reporting Register of CR0 Bits

Fixed to 1 (R/O)

See Appendix A.7, “VMX-Fixed Bits in CR0.”

If CPUID.01H:ECX.[5] = 1

488H

1160

IA32_VMX_CR4_FIXED0

Capability Reporting Register of CR4 Bits

Fixed to 0 (R/O)

See Appendix A.8, “VMX-Fixed Bits in CR4.”

If CPUID.01H:ECX.[5] = 1

Table 35-2. IA-32 Architectural MSRs (Contd.)

Register

Address

Architectural MSR Name and bit

fields

(Former MSR Name)

MSR/Bit Description

Comment

Hex

Decimal