34-4 Vol. 3C

SYSTEM MANAGEMENT MODE

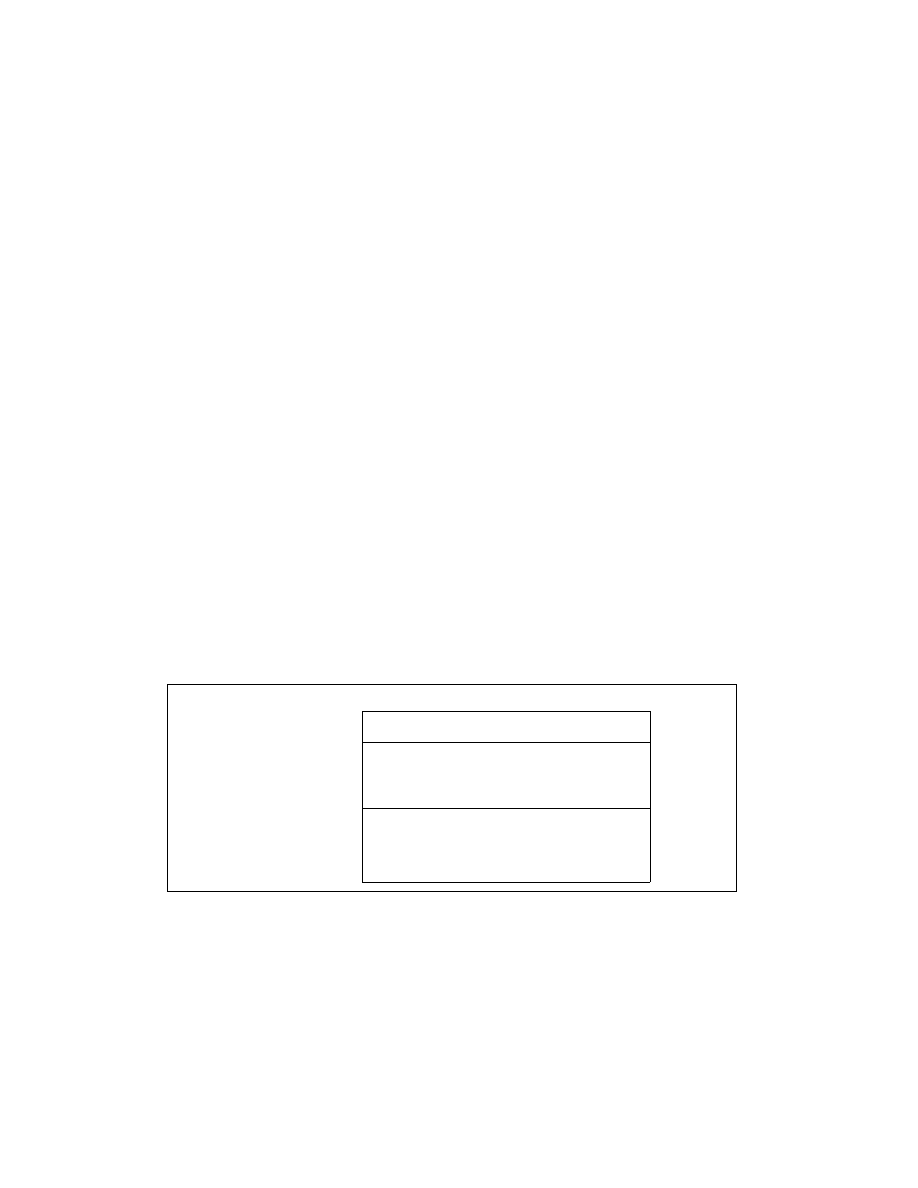

The default SMRAM size is 64 KBytes beginning at a base physical address in physical memory called the SMBASE

(see Figure 34-1). The SMBASE default value following a hardware reset is 30000H. The processor looks for the

first instruction of the SMI handler at the address [SMBASE + 8000H]. It stores the processor’s state in the area

from [SMBASE + FE00H] to [SMBASE + FFFFH]. See Section 34.4.1 for a description of the mapping of the state

save area.

The system logic is minimally required to decode the physical address range for the SMRAM from [SMBASE +

8000H] to [SMBASE + FFFFH]. A larger area can be decoded if needed. The size of this SMRAM can be between 32

KBytes and 4 GBytes.

The location of the SMRAM can be changed by changing the SMBASE value (see Section 34.11). It should be noted

that all processors in a multiple-processor system are initialized with the same SMBASE value (30000H). Initializa-

tion software must sequentially place each processor in SMM and change its SMBASE so that it does not overlap

those of other processors.

The actual physical location of the SMRAM can be in system memory or in a separate RAM memory. The processor

generates an SMI acknowledge transaction (P6 family processors) or asserts the SMIACT# pin (Pentium and

Intel486 processors) when the processor receives an SMI (see Section 34.3.1).

System logic can use the SMI acknowledge transaction or the assertion of the SMIACT# pin to decode accesses to

the SMRAM and redirect them (if desired) to specific SMRAM memory. If a separate RAM memory is used for

SMRAM, system logic should provide a programmable method of mapping the SMRAM into system memory space

when the processor is not in SMM. This mechanism will enable start-up procedures to initialize the SMRAM space

(that is, load the SMI handler) before executing the SMI handler during SMM.

34.4.1

SMRAM State Save Map

When an IA-32 processor that does not support Intel 64 architecture initially enters SMM, it writes its state to the

state save area of the SMRAM. The state save area begins at [SMBASE + 8000H + 7FFFH] and extends down to

[SMBASE + 8000H + 7E00H]. Table 34-1 shows the state save map. The offset in column 1 is relative to the

SMBASE value plus 8000H. Reserved spaces should not be used by software.

Some of the registers in the SMRAM state save area (marked YES in column 3) may be read and changed by the

SMI handler, with the changed values restored to the processor registers by the RSM instruction. Some register

images are read-only, and must not be modified (modifying these registers will result in unpredictable behavior).

An SMI handler should not rely on any values stored in an area that is marked as reserved.

Figure 34-1. SMRAM Usage

Start of State Save Area

SMBASE + FFFFH

SMBASE

SMBASE + 8000H

SMRAM

SMI Handler Entry Point