Vol. 3C 34-5

SYSTEM MANAGEMENT MODE

The following registers are saved (but not readable) and restored upon exiting SMM:

•

Control register CR4. (This register is cleared to all 0s when entering SMM).

•

The hidden segment descriptor information stored in segment registers CS, DS, ES, FS, GS, and SS.

If an SMI request is issued for the purpose of powering down the processor, the values of all reserved locations in

the SMM state save must be saved to nonvolatile memory.

The following state is not automatically saved and restored following an SMI and the RSM instruction, respectively:

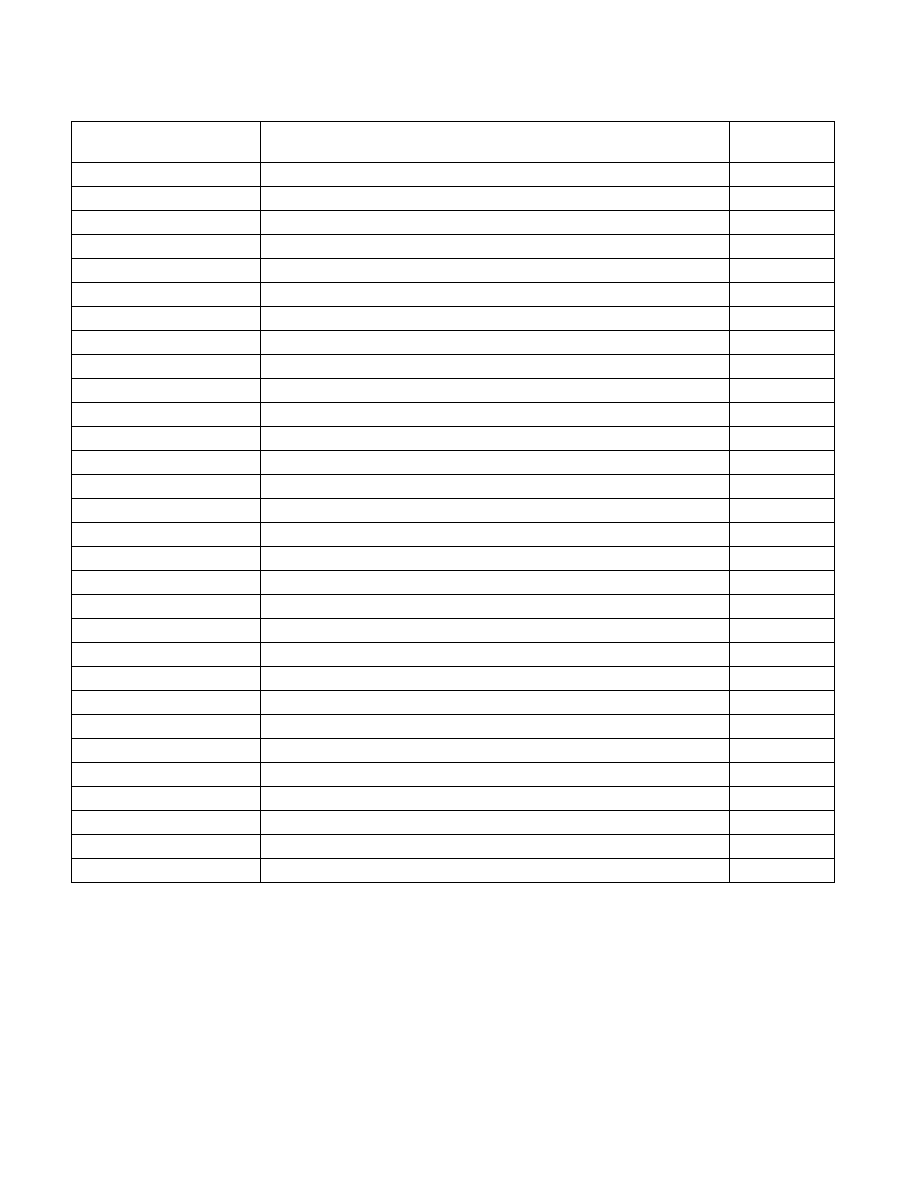

Table 34-1. SMRAM State Save Map

Offset

(Added to SMBASE + 8000H)

Register

Writable?

7FFCH

CR0

No

7FF8H

CR3

No

7FF4H

EFLAGS

Yes

7FF0H

EIP

Yes

7FECH

EDI

Yes

7FE8H

ESI

Yes

7FE4H

EBP

Yes

7FE0H

ESP

Yes

7FDCH

EBX

Yes

7FD8H

EDX

Yes

7FD4H

ECX

Yes

7FD0H

EAX

Yes

7FCCH

DR6

No

7FC8H

DR7

No

7FC4H

TR

1

No

7FC0H

Reserved

No

7FBCH

GS

1

No

7FB8H

FS

1

No

7FB4H

DS

1

No

7FB0H

SS

1

No

7FACH

CS

1

No

7FA8H

ES

1

No

7FA4H

I/O State Field, see Section 34.7

No

7FA0H

I/O Memory Address Field, see Section 34.7

No

7F9FH-7F03H

Reserved

No

7F02H

Auto HALT Restart Field (Word)

Yes

7F00H

I/O Instruction Restart Field (Word)

Yes

7EFCH

SMM Revision Identifier Field (Doubleword)

No

7EF8H

SMBASE Field (Doubleword)

Yes

7EF7H - 7E00H

Reserved

No

NOTE:

1. The two most significant bytes are reserved.