24-10 Vol. 3C

VIRTUAL MACHINE CONTROL STRUCTURES

All other bits in this field are reserved, some to 0 and some to 1. Software should consult the VMX capability MSRs

IA32_VMX_PROCBASED_CTLS and IA32_VMX_TRUE_PROCBASED_CTLS (see Appendix A.3.2) to determine how

to set reserved bits. Failure to set reserved bits properly causes subsequent VM entries to fail (see Section

26.2.1.1).

The first processors to support the virtual-machine extensions supported only the 1-settings of bits 1, 4–6, 8, 13–

16, and 26. The VMX capability MSR IA32_VMX_PROCBASED_CTLS will always report that these bits must be 1.

Logical processors that support the 0-settings of any of these bits will support the VMX capability MSR

IA32_VMX_TRUE_PROCBASED_CTLS MSR, and software should consult this MSR to discover support for the 0-

settings of these bits. Software that is not aware of the functionality of any one of these bits should set that bit to 1.

Bit 31 of the primary processor-based VM-execution controls determines whether the secondary processor-based

VM-execution controls are used. If that bit is 0, VM entry and VMX non-root operation function as if all the

secondary processor-based VM-execution controls were 0. Processors that support only the 0-setting of bit 31 of

the primary processor-based VM-execution controls do not support the secondary processor-based VM-execution

controls.

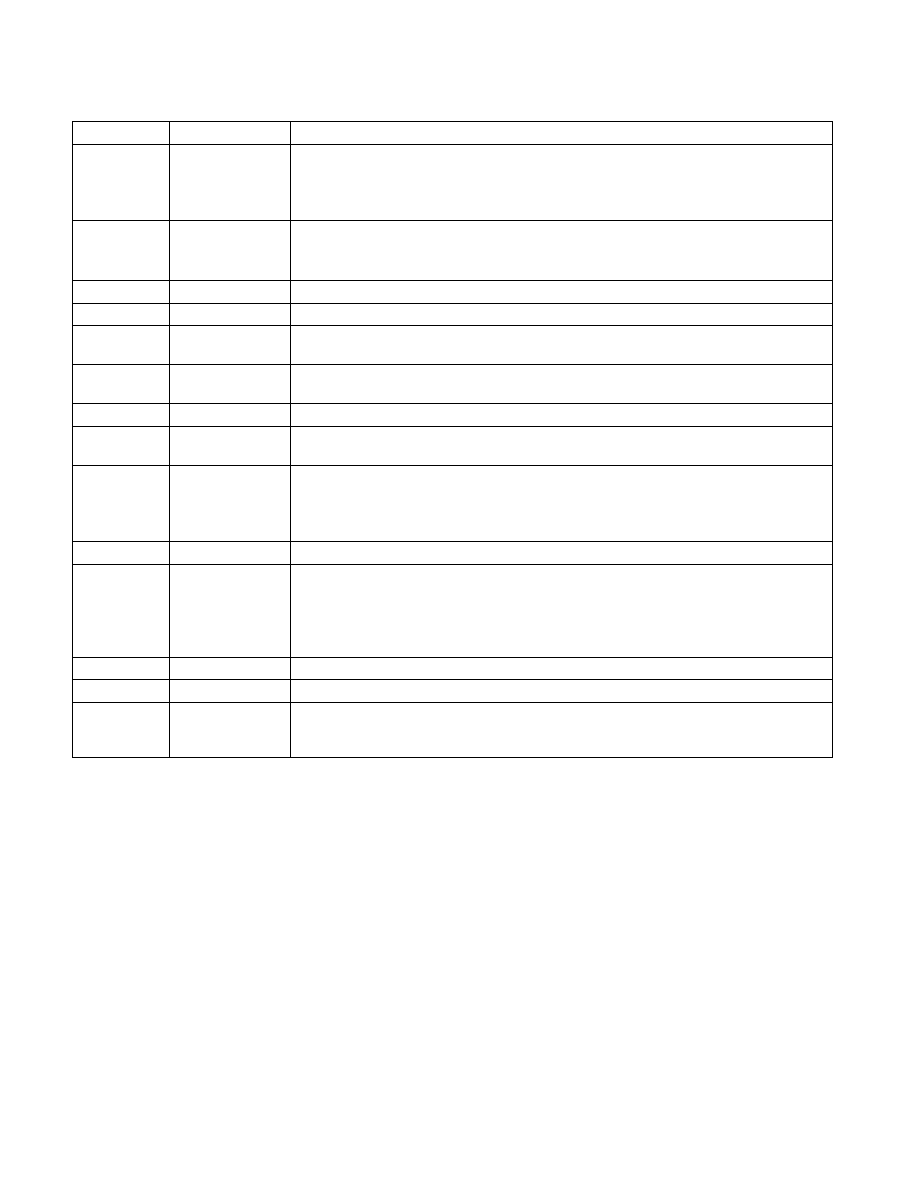

15

CR3-load exiting

In conjunction with the CR3-target controls (see Section 24.6.7), this control determines

whether executions of MOV to CR3 cause VM exits. See Section 25.1.3.

The first processors to support the virtual-machine extensions supported only the 1-setting

of this control.

16

CR3-store exiting

This control determines whether executions of MOV from CR3 cause VM exits.

The first processors to support the virtual-machine extensions supported only the 1-setting

of this control.

19

CR8-load exiting

This control determines whether executions of MOV to CR8 cause VM exits.

20

CR8-store exiting

This control determines whether executions of MOV from CR8 cause VM exits.

21

Use TPR shadow

Setting this control to 1 enables TPR virtualization and other APIC-virtualization features. See

22

NMI-window

exiting

If this control is 1, a VM exit occurs at the beginning of any instruction if there is no virtual-

NMI blocking (see Section 24.4.2).

23

MOV-DR exiting

This control determines whether executions of MOV DR cause VM exits.

24

Unconditional I/O

exiting

This control determines whether executions of I/O instructions (IN, INS/INSB/INSW/INSD, OUT,

and OUTS/OUTSB/OUTSW/OUTSD) cause VM exits.

25

Use I/O bitmaps

This control determines whether I/O bitmaps are used to restrict executions of I/O instructions

(see Section 24.6.4 and Section 25.1.3).

For this control, “0” means “do not use I/O bitmaps” and “1” means “use I/O bitmaps.” If the I/O

bitmaps are used, the setting of the “unconditional I/O exiting” control is ignored.

27

Monitor trap flag

If this control is 1, the monitor trap flag debugging feature is enabled. See Section 25.5.2.

28

Use MSR bitmaps

This control determines whether MSR bitmaps are used to control execution of the RDMSR

and WRMSR instructions (see Section 24.6.9 and Section 25.1.3).

For this control, “0” means “do not use MSR bitmaps” and “1” means “use MSR bitmaps.” If the

MSR bitmaps are not used, all executions of the RDMSR and WRMSR instructions cause

VM exits.

29

MONITOR exiting

This control determines whether executions of MONITOR cause VM exits.

30

PAUSE exiting

This control determines whether executions of PAUSE cause VM exits.

31

Activate secondary

controls

This control determines whether the secondary processor-based VM-execution controls are

used. If this control is 0, the logical processor operates as if all the secondary processor-based

VM-execution controls were also 0.

Table 24-6. Definitions of Primary Processor-Based VM-Execution Controls (Contd.)

Bit Position(s) Name

Description