10-2 Vol. 1

PROGRAMMING WITH INTEL® STREAMING SIMD EXTENSIONS (INTEL® SSE)

SSE extensions are fully compatible with all software written for IA-32 processors. All existing software continues

to run correctly, without modification, on processors that incorporate SSE extensions. Enhancements to CPUID

permit detection of SSE extensions. SSE extensions are accessible from all IA-32 execution modes: protected

mode, real address mode, and virtual-8086 mode.

The following sections of this chapter describe the programming environment for SSE extensions, including: XMM

registers, the packed single-precision floating-point data type, and SSE instructions. For additional information,

see:

•

Section 11.6, “Writing Applications with SSE/SSE2 Extensions”.

•

Section 11.5, “SSE, SSE2, and SSE3 Exceptions,” describes the exceptions that can be generated with

SSE/SSE2/SSE3 instructions.

•

Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volumes 2A & 2B, provide a detailed

description of these instructions.

•

Chapter 13, “System Programming for Instruction Set Extensions and Processor Extended States,” in the

Intel® 64 and IA-32 Architectures Software Developer’s Manual, Volume 3A, gives guidelines for integrating

these extensions into an operating-system environment.

10.2 SSE

PROGRAMMING

ENVIRONMENT

Figure 10-1 shows the execution environment for the SSE extensions. All SSE instructions operate on the XMM

registers, MMX registers, and/or memory as follows:

•

XMM registers — These eight registers (see Figure 10-2 and Section 10.2.2, “XMM Registers”) are used to

operate on packed or scalar single-precision floating-point data. Scalar operations are operations performed on

individual (unpacked) single-precision floating-point values stored in the low doubleword of an XMM register.

XMM registers are referenced by the names XMM0 through XMM7.

•

MXCSR register — This 32-bit register (see Figure 10-3 and Section 10.2.3, “MXCSR Control and Status

Register”) provides status and control bits used in SIMD floating-point operations.

•

MMX registers — These eight registers (see Figure 9-2) are used to perform operations on 64-bit packed

integer data. They are also used to hold operands for some operations performed between the MMX and XMM

registers. MMX registers are referenced by the names MM0 through MM7.

•

General-purpose registers — The eight general-purpose registers (see Figure 3-5) are used along with the

existing IA-32 addressing modes to address operands in memory. (MMX and XMM registers cannot be used to

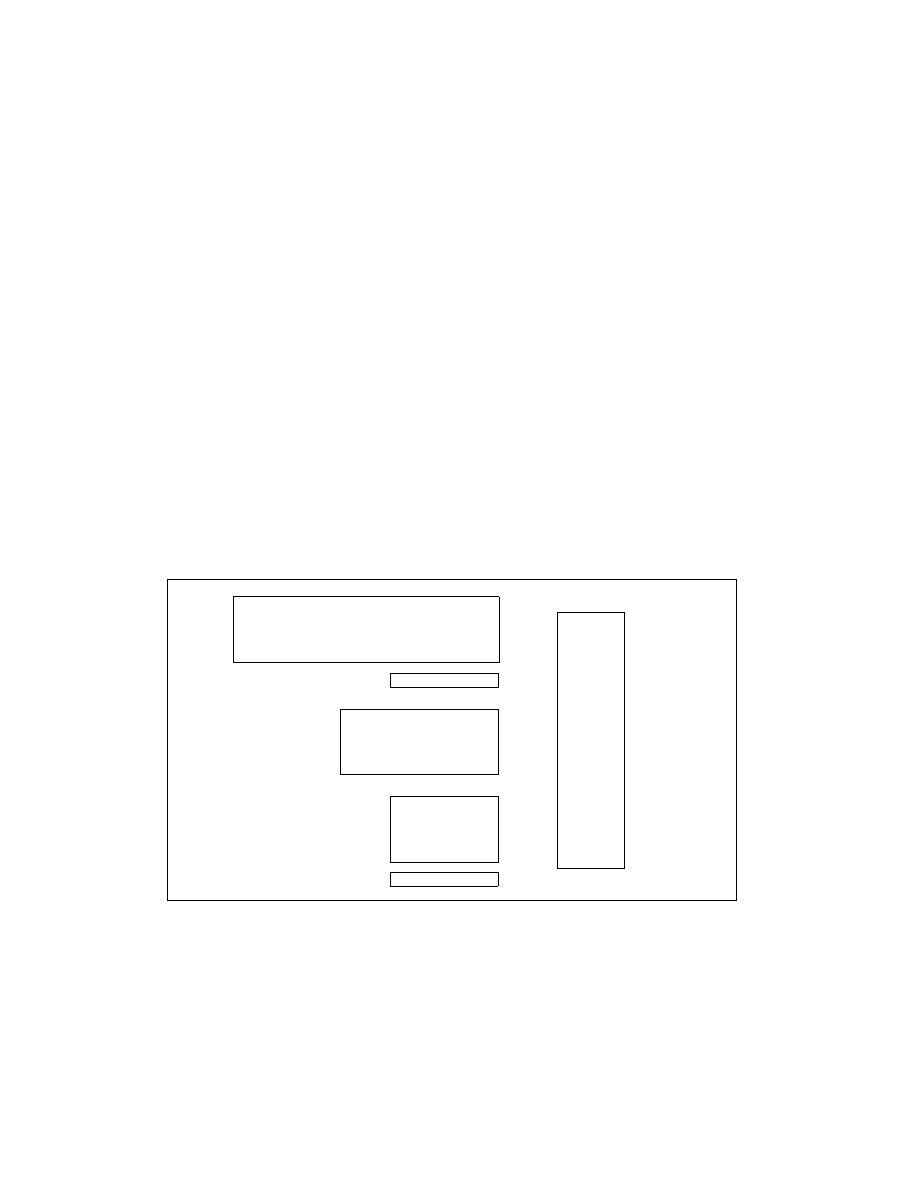

Figure 10-1. SSE Execution Environment

0

2

32

-1

Eight 32-Bit

32 Bits

EFLAGS Register

Address Space

General-Purpose

Eight 64-Bit

MMX Registers

Eight 128-Bit

XMM Registers

32 Bits

MXCSR Register

Registers