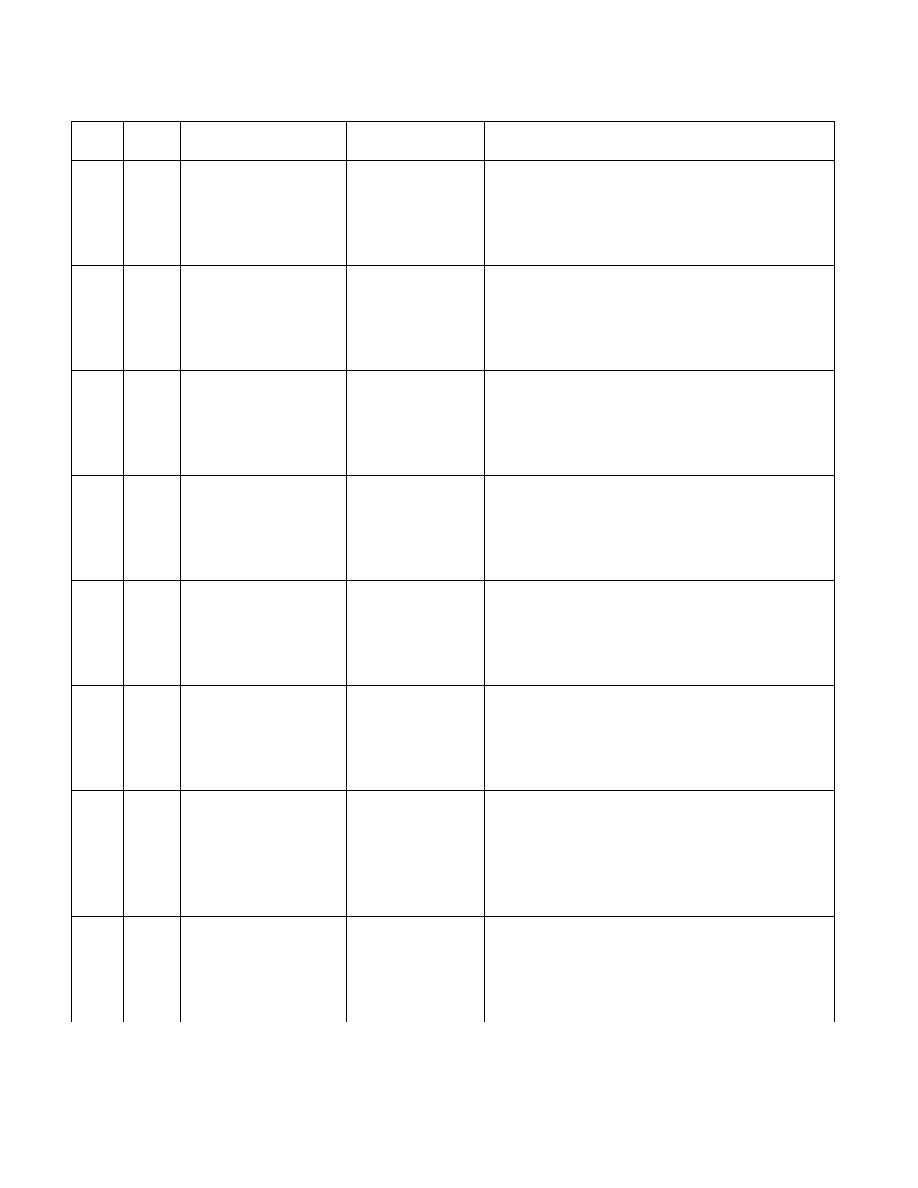

Vol. 3B 19-129

PERFORMANCE-MONITORING EVENTS

6BH

See

and

18-3.

BUS_TRANS

_P.(Core and Bus Agents)

Partial bus

transactions.

This event counts all (read and write) partial bus

transactions.

6CH

See

and

18-3.

BUS_TRANS_IO.(Core and

Bus Agents)

IO bus transactions.

This event counts the number of completed I/O bus

transactions as a result of IN and OUT instructions. The

count does not include memory mapped IO.

6DH

See

and

18-3.

BUS_TRANS_

DEF.(Core and Bus Agents)

Deferred bus

transactions.

This event counts the number of deferred transactions.

6E

H

See

and

18-3.

BUS_TRANS_

BURST.(Core and Bus

Agents)

Burst (full cache-line)

bus transactions.

This event counts burst (full cache line) transactions

including:

• Burst reads.

• RFOs.

• Explicit writebacks.

• Write combine lines.

6FH

See

and

18-3.

BUS_TRANS_

MEM.(Core and Bus Agents)

Memory bus

transactions.

This event counts all memory bus transactions including:

• Burst transactions.

• Partial reads and writes - invalidate transactions.

The BUS_TRANS_MEM count is the sum of

BUS_TRANS_BURST, BUS_TRANS_P and BUS_TRANS_IVAL.

70H

See

and

18-3.

BUS_TRANS_

ANY.(Core and Bus Agents)

All bus transactions.

This event counts all bus transactions. This includes:

• Memory transactions.

• IO transactions (non memory-mapped).

• Deferred transaction completion.

• Other less frequent transactions, such as interrupts.

77H

See

and

18-6.

EXT_SNOOP.

(Bus Agents, Snoop

Response)

External snoops.

This event counts the snoop responses to bus transactions.

Responses can be counted separately by type and by bus

agent.

With the 'THIS_AGENT' mask, the event counts snoop

responses from this processor to bus transactions sent by

this processor. With the 'ALL_AGENTS' mask the event

counts all snoop responses seen on the bus.

78H

See

and

18-7.

CMP_SNOOP.(Core, Snoop

Type)

L1 data cache

snooped by other core.

This event counts the number of times the L1 data cache is

snooped for a cache line that is needed by the other core in

the same processor. The cache line is either missing in the

L1 instruction or data caches of the other core, or is

available for reading only and the other core wishes to write

the cache line.

Table 19-23. Non-Architectural Performance Events in Processors Based on Intel® Core™ Microarchitecture (Contd.)

Event

Num

Umask

Value

Event Name

Definition

Description and

Comment