Vol. 3B 18-107

PERFORMANCE MONITORING

two logical processors in the same core share performance monitoring resources (see Section 18.16, “Performance

Monitoring and Intel Hyper-Threading Technology in Processors Based on Intel NetBurst

18.20 PERFORMANCE MONITORING ON 64-BIT INTEL XEON PROCESSOR MP

WITH UP TO 8-MBYTE L3 CACHE

The 64-bit Intel Xeon processor MP with up to 8-MByte L3 cache has a CPUID signature of family [0FH], model

[03H or 04H]. Performance monitoring capabilities available to Pentium 4 and Intel Xeon processors with the same

values (see Section 18.1 and Section 18.16) apply to the 64-bit Intel Xeon processor MP with an L3 cache.

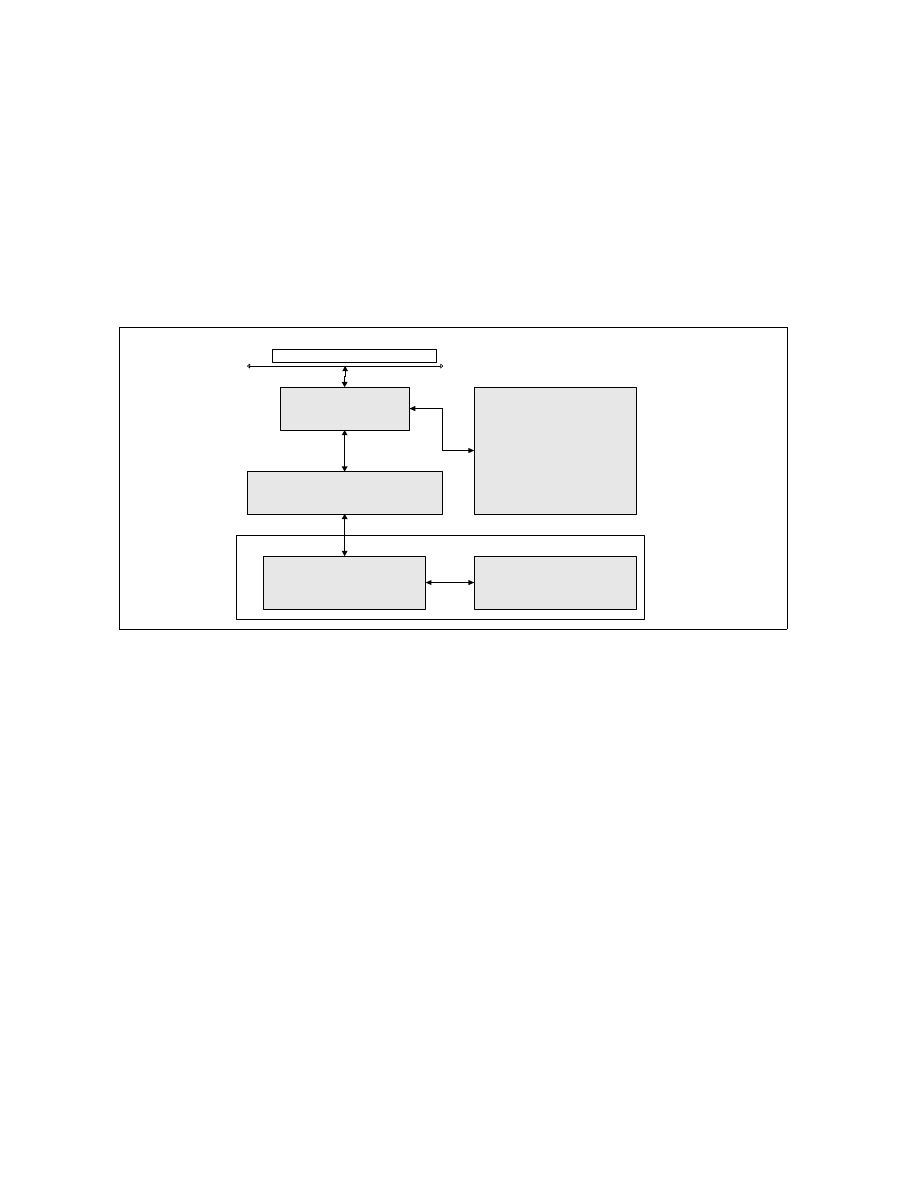

The level 3 cache is connected between the system bus and IOQ through additional control logic. See Figure 18-50.

Additional performance monitoring capabilities and facilities unique to 64-bit Intel Xeon processor MP with an L3

cache are described in this section. The facility for monitoring events consists of a set of dedicated model-specific

registers (MSRs), each dedicated to a specific event. Programming of these MSRs requires using RDMSR/WRMSR

instructions with 64-bit values.

The lower 32-bits of the MSRs at addresses 107CC through 107D3 are treated as 32 bit performance counter regis-

ters. These performance counters can be accessed using RDPMC instruction with the index starting from 18

through 25. The EDX register returns zero when reading these 8 PMCs.

The performance monitoring capabilities consist of four events. These are:

•

IBUSQ event — This event detects the occurrence of micro-architectural conditions related to the iBUSQ unit.

It provides two MSRs: MSR_IFSB_IBUSQ0 and MSR_IFSB_IBUSQ1. Configure sub-event qualification and

enable/disable functions using the high 32 bits of these MSRs. The low 32 bits act as a 32-bit event counter.

Counting starts after software writes a non-zero value to one or more of the upper 32 bits. See Figure 18-51.

Figure 18-50. Block Diagram of 64-bit Intel Xeon Processor MP with 8-MByte L3

iBUSQ and iSNPQ

System Bus

3rd Level Cache

8 or 4 -way

IOQ

iFSB

Processor Core

(Front end, Execution,

Retirement, L1, L2