18-108 Vol. 3B

PERFORMANCE MONITORING

•

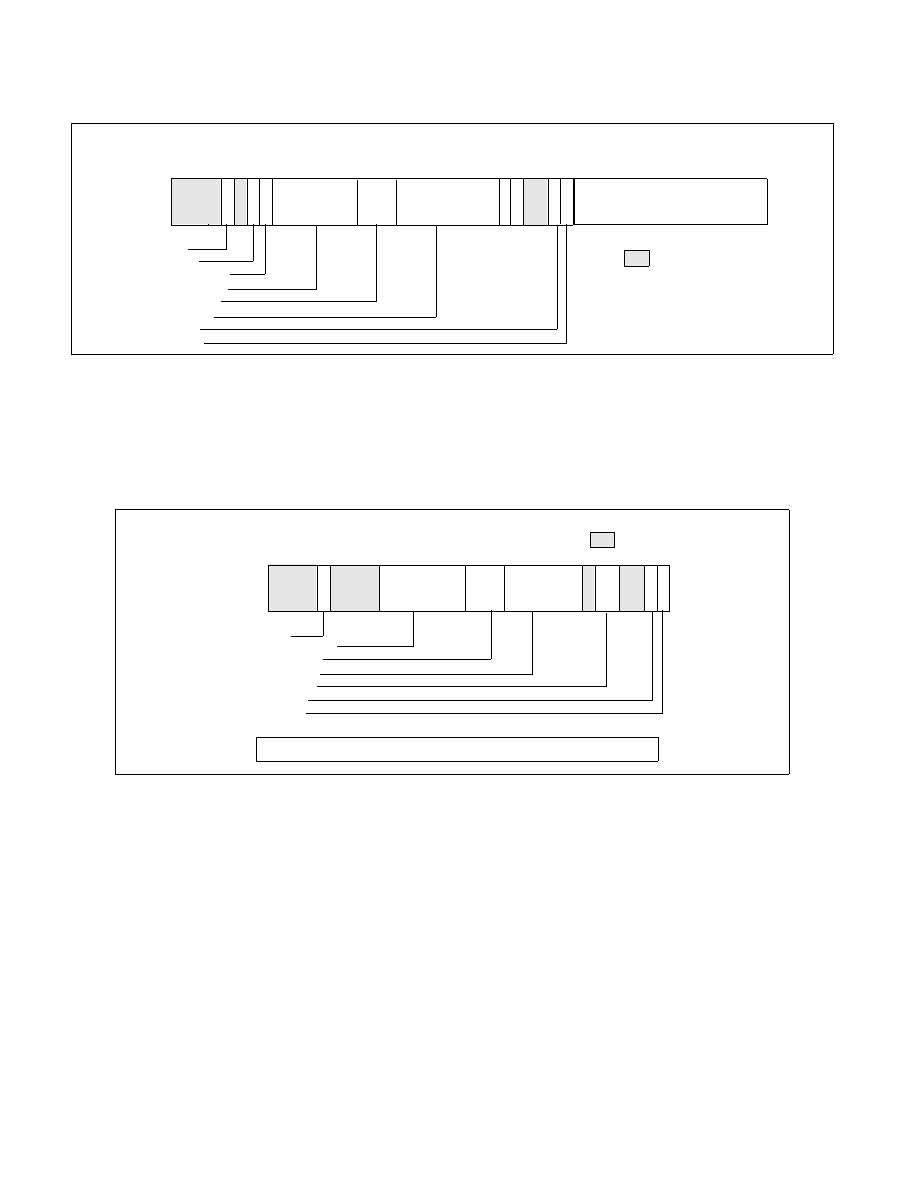

ISNPQ event — This event detects the occurrence of microarchitectural conditions related to the iSNPQ unit.

It provides two MSRs: MSR_IFSB_ISNPQ0 and MSR_IFSB_ISNPQ1. Configure sub-event qualifications and

enable/disable functions using the high 32 bits of the MSRs. The low 32-bits act as a 32-bit event counter.

Counting starts after software writes a non-zero value to one or more of the upper 32-bits. See Figure 18-52.

•

EFSB event — This event can detect the occurrence of micro-architectural conditions related to the iFSB unit

or system bus. It provides two MSRs: MSR_EFSB_DRDY0 and MSR_EFSB_DRDY1. Configure sub-event qualifi-

cations and enable/disable functions using the high 32 bits of the 64-bit MSR. The low 32-bit act as a 32-bit

event counter. Counting starts after software writes a non-zero value to one or more of the qualification bits in

the upper 32-bits of the MSR. See Figure 18-53.

Figure 18-51. MSR_IFSB_IBUSQx, Addresses: 107CCH and 107CDH

Figure 18-52. MSR_IFSB_ISNPQx, Addresses: 107CEH and 107CFH

L3_state_match

46

38

45

37 36

33

34

Saturate

Fill_match

Eviction_match

Snoop_match

Type_match

T1_match

T0_match

Reserved

63

56 55

48

32

49

57

58

59

60

35

1 1

32 bit event count

MSR_IFSB_IBUSQx, Addresses: 107CCH and 107CDH

31

0

L3_state_match

46

38

45

37 36

33

34

Saturate

Snoop_match

Type_match

T1_match

T0_match

Reserved

63

56 55

48

32

57

58

59

60

35

39

Agent_match

MSR_IFSB_ISNPQx, Addresses: 107CEH and 107CFH

32 bit event count

0

31