18-92 Vol. 3B

PERFORMANCE MONITORING

18.15.5.3 Starting Event Counting

Event counting by a performance counter can be initiated in either of two ways. The typical way is to set the enable

flag in the counter’s CCCR. Following the instruction to set the enable flag, event counting begins and continues

until it is stopped (see Section 18.15.5.5, “Halting Event Counting”).

The following procedural step shows how to start event counting. This step is a continuation of the setup procedure

introduced in Section 18.15.5.2, “Filtering Events.”

9. To start event counting, use the WRMSR instruction to set the CCCR enable flag for the performance counter.

This setup procedure is continued in the next section, Section 18.15.5.4, “Reading a Performance Counter’s Count.”

The second way that a counter can be started by using the cascade feature. Here, the overflow of one counter auto-

matically starts its alternate counter (see Section 18.15.5.6, “Cascading Counters”).

18.15.5.4 Reading a Performance Counter’s Count

Performance counters can be read using either the RDPMC or RDMSR instructions. The enhanced functions of the

RDPMC instruction (including fast read) are described in Section 18.15.2, “Performance Counters.” These instruc-

tions can be used to read a performance counter while it is counting or when it is stopped.

The following procedural step shows how to read the event counter. This step is a continuation of the setup proce-

dure introduced in Section 18.15.5.3, “Starting Event Counting.”

10. To read a performance counters current event count, execute the RDPMC instruction with the counter number

obtained from Table 18-63 used as an operand.

This setup procedure is continued in the next section, Section 18.15.5.5, “Halting Event Counting.”

18.15.5.5 Halting Event Counting

After a performance counter has been started (enabled), it continues counting indefinitely. If the counter overflows

(goes one count past its maximum count), it wraps around and continues counting. When the counter wraps

around, it sets its OVF flag to indicate that the counter has overflowed. The OVF flag is a sticky flag that indicates

that the counter has overflowed at least once since the OVF bit was last cleared.

To halt counting, the CCCR enable flag for the counter must be cleared.

The following procedural step shows how to stop event counting. This step is a continuation of the setup procedure

introduced in Section 18.15.5.4, “Reading a Performance Counter’s Count.”

11. To stop event counting, execute a WRMSR instruction to clear the CCCR enable flag for the performance

counter.

To halt a cascaded counter (a counter that was started when its alternate counter overflowed), either clear the

Cascade flag in the cascaded counter’s CCCR MSR or clear the OVF flag in the alternate counter’s CCCR MSR.

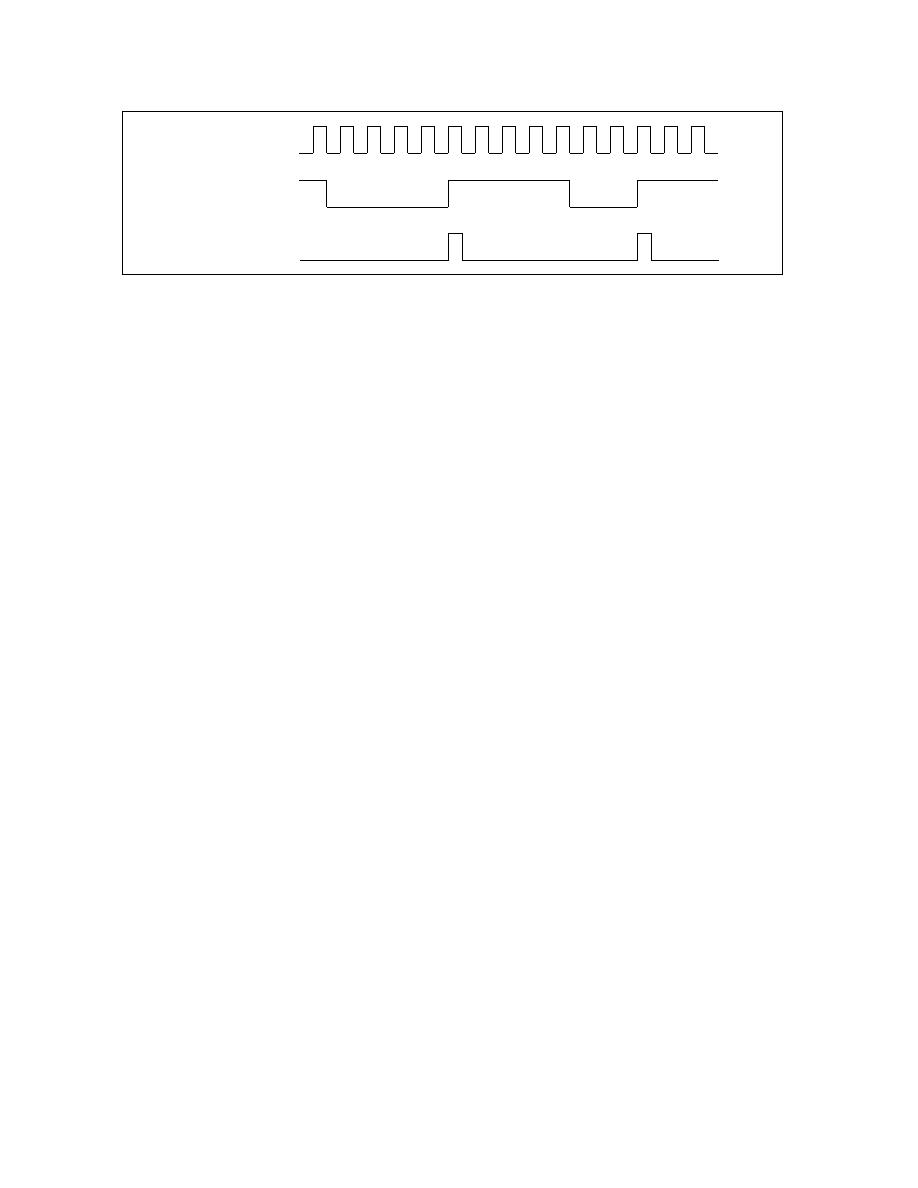

Figure 18-46. Effects of Edge Filtering

Output from

Threshold Filter

Counter Increments

On Rising Edge

(False-to-True)

Processor Clock