Vol. 3A 2-9

SYSTEM ARCHITECTURE OVERVIEW

2.2.1

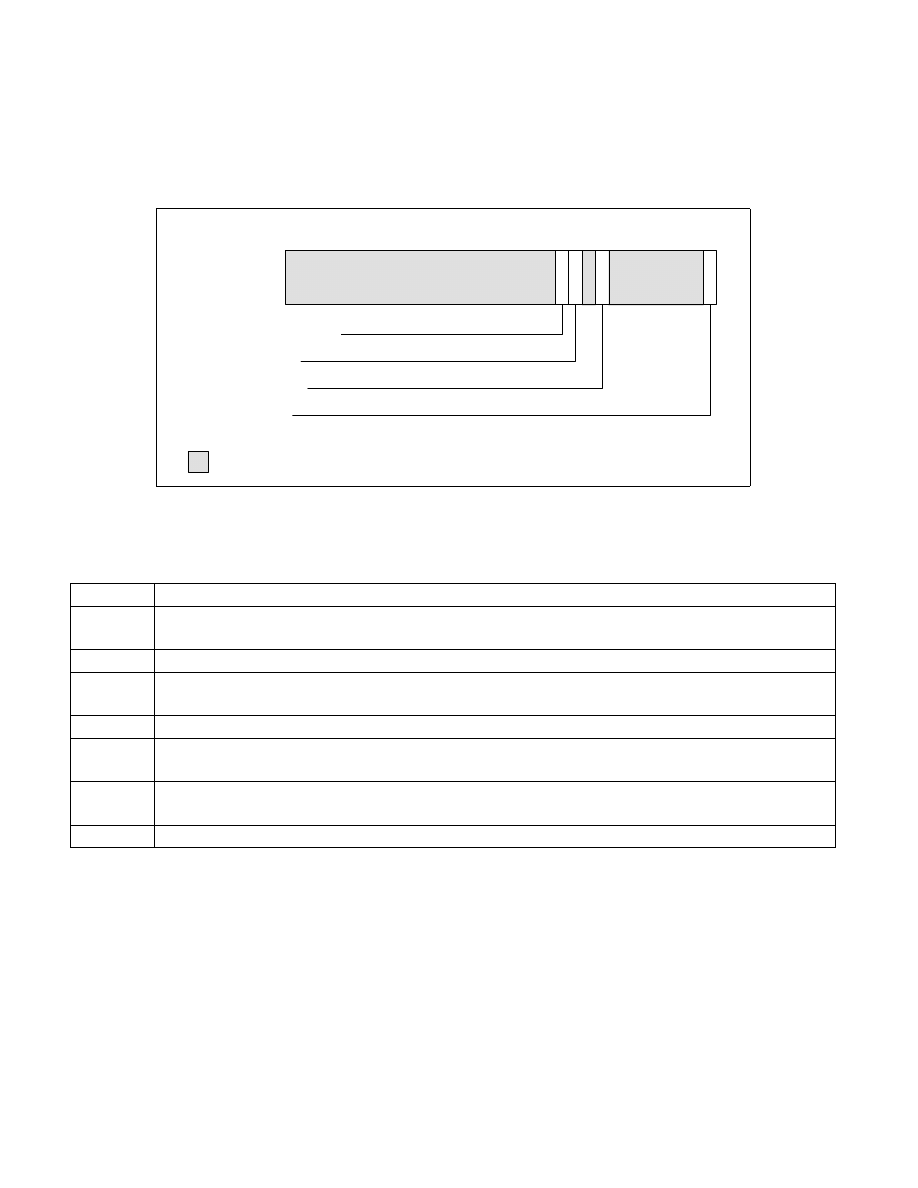

Extended Feature Enable Register

The IA32_EFER MSR provides several fields related to IA-32e mode enabling and operation. It also provides one

field that relates to page-access right modification (see

). The layout of the

IA32_EFER MSR is shown in Figure 2-4.

2.3

SYSTEM FLAGS AND FIELDS IN THE EFLAGS REGISTER

The system flags and IOPL field of the EFLAGS register control I/O, maskable hardware interrupts, debugging, task

switching, and the virtual-8086 mode (see Figure 2-5). Only privileged code (typically operating system or execu-

tive code) should be allowed to modify these bits.

The system flags and IOPL are:

TF

Trap (bit 8) — Set to enable single-step mode for debugging; clear to disable single-step mode. In single-

step mode, the processor generates a debug exception after each instruction. This allows the execution

state of a program to be inspected after each instruction. If an application program sets the TF flag using a

Figure 2-4. IA32_EFER MSR Layout

Table 2-1. IA32_EFER MSR Information

Bit

Description

0

SYSCALL Enable: IA32_EFER.SCE (R/W)

Enables SYSCALL/SYSRET instructions in 64-bit mode.

7:1

Reserved.

8

IA-32e Mode Enable: IA32_EFER.LME (R/W)

Enables IA-32e mode operation.

9

Reserved.

10

IA-32e Mode Active: IA32_EFER.LMA (R)

Indicates IA-32e mode is active when set.

11

Execute Disable Bit Enable: IA32_EFER.NXE (R/W)

Enables page access restriction by preventing instruction fetches from PAE pages with the XD bit set (See Section 4.6).

63:12

Reserved.

Reserved

IA-32e Mode Active

0

1

7

8

9

10

11

12

63

IA32_EFER

IA-32e Mode Enable

Execute Disable Bit Enable

SYSCALL Enable