Vol. 3B 18-51

PERFORMANCE MONITORING

18.9.1

Global Counter Control Facilities In Intel

®

Microarchitecture Code Name Sandy Bridge

The number of general-purpose performance counters visible to a logical processor can vary across Processors

based on Intel microarchitecture code name Sandy Bridge. Software must use CPUID to determine the number

performance counters/event select registers (See Section 18.2.1.1).

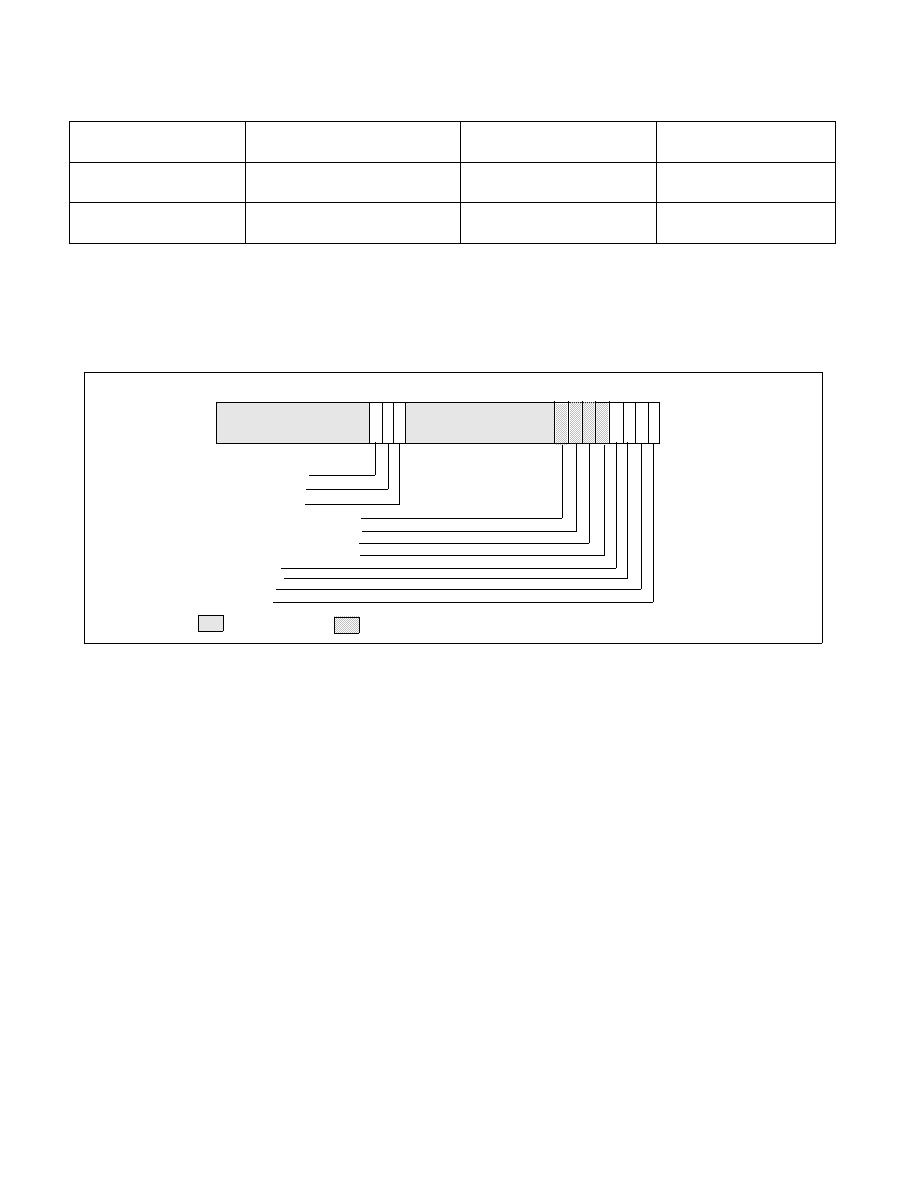

Figure 18-15 depicts the layout of IA32_PERF_GLOBAL_CTRL MSR. The enable bits (PMC4_EN, PMC5_EN,

PMC6_EN, PMC7_EN) corresponding to IA32_PMC4-IA32_PMC7 are valid only if CPUID.0AH:EAX[15:8] reports a

value of ‘8’. If CPUID.0AH:EAX[15:8] = 4, attempts to set the invalid bits will cause #GP.

Each enable bit in IA32_PERF_GLOBAL_CTRL is AND’ed with the enable bits for all privilege levels in the respective

IA32_PERFEVTSELx or IA32_PERF_FIXED_CTR_CTRL MSRs to start/stop the counting of respective counters.

Counting is enabled if the AND’ed results is true; counting is disabled when the result is false.

IA32_PERF_GLOBAL_STATUS MSR provides single-bit status used by software to query the overflow condition of

each performance counter. IA32_PERF_GLOBAL_STATUS[bit 62] indicates overflow conditions of the DS area data

buffer (see Figure 18-33). A value of 1 in each bit of the PMCx_OVF field indicates an overflow condition has

occurred in the associated counter.

PEBS-PDIR

Yes (using precise

INST_RETIRED.ALL).

No

Off-core Response Event

MSR 1A6H and 1A7H, extended

request and response types.

MSR 1A6H and 1A7H, limited

response types.

Nehalem supports 1A6H

only.

Figure 18-32. IA32_PERF_GLOBAL_CTRL MSR in Intel® Microarchitecture Code Name Sandy Bridge

Table 18-30. Core PMU Comparison (Contd.)

Box

Intel® microarchitecture code

name Sandy Bridge

Intel® microarchitecture code

name Westmere

Comment

FIXED_CTR2 enable

FIXED_CTR1 enable

FIXED_CTR0 enable

PMC7_EN (if PMC7 present)

2 1 0

PMC6_EN (if PMC6 present)

31

32

33

34

35

Reserved

63

PMC5_EN (if PMC5 present)

PMC4_EN (if PMC4 present)

PMC3_EN

PMC2_EN

PMC1_EN

Valid if CPUID.0AH:EAX[15:8] = 8, else reserved.

PMC0_EN

8 7 6 5 4 3