18-52 Vol. 3B

PERFORMANCE MONITORING

When a performance counter is configured for PEBS, an overflow condition in the counter will arm PEBS. On the

subsequent event following overflow, the processor will generate a PEBS event. On a PEBS event, the processor will

perform bounds checks based on the parameters defined in the DS Save Area (see Section 17.4.9). Upon

successful bounds checks, the processor will store the data record in the defined buffer area, clear the counter

overflow status, and reload the counter. If the bounds checks fail, the PEBS will be skipped entirely. In the event

that the PEBS buffer fills up, the processor will set the OvfBuffer bit in MSR_PERF_GLOBAL_STATUS.

IA32_PERF_GLOBAL_OVF_CTL MSR allows software to clear overflow the indicators for general-purpose or fixed-

function counters via a single WRMSR (see Figure 18-34). Clear overflow indications when:

•

Setting up new values in the event select and/or UMASK field for counting or interrupt based sampling

•

Reloading counter values to continue sampling

•

Disabling event counting or interrupt based sampling

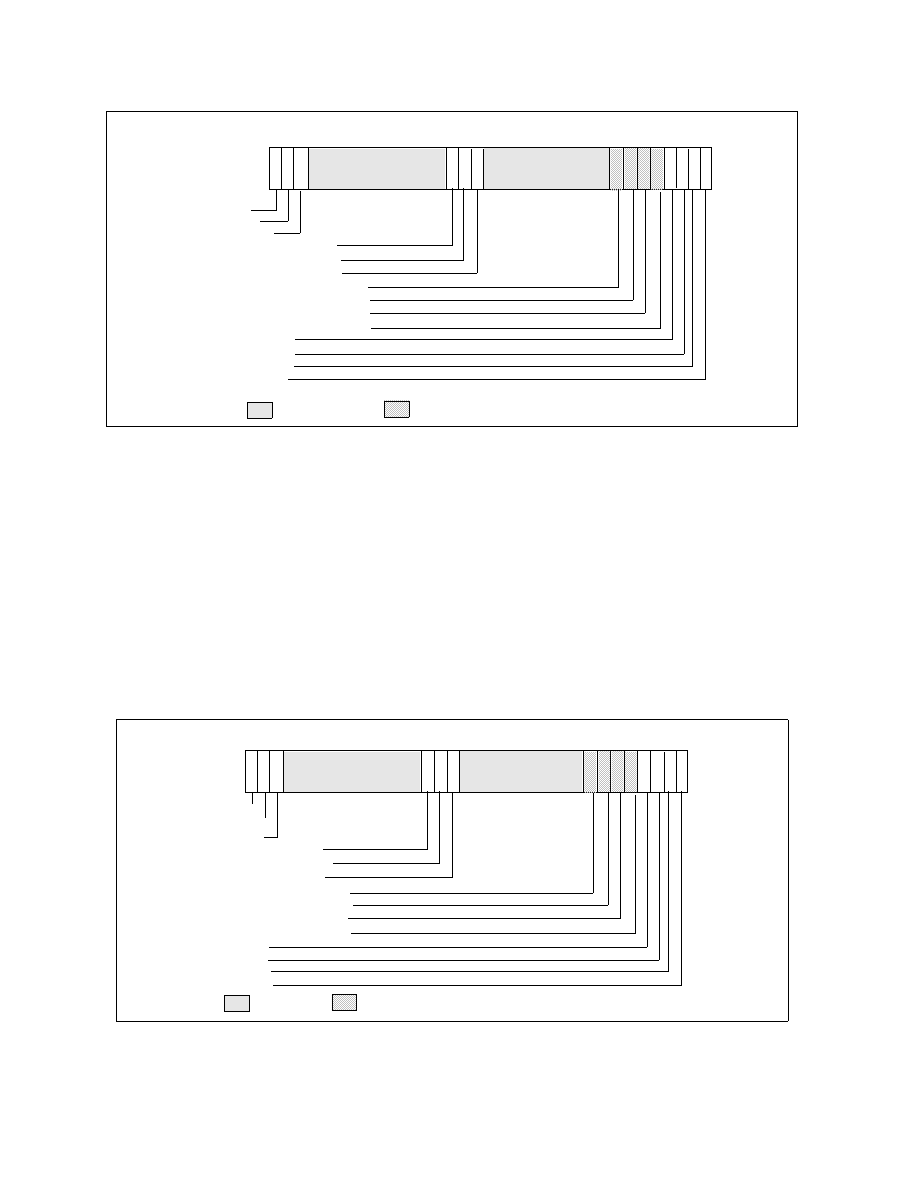

Figure 18-33. IA32_PERF_GLOBAL_STATUS MSR in Intel® Microarchitecture Code Name Sandy Bridge

Figure 18-34. IA32_PERF_GLOBAL_OVF_CTRL MSR in Intel microarchitecture code name Sandy Bridge

62

FIXED_CTR2 Overflow (RO)

FIXED_CTR1 Overflow (RO)

FIXED_CTR0 Overflow (RO)

PMC7_OVF (RO, If PMC7 present)

2 1 0

PMC6_OVF (RO, If PMC6 present)

31

32

33

34

35

Reserved

63

CondChgd

Ovf_DSBuffer

8 7 6 5 4 3

PMC5_OVF (RO, If PMC5 present)

PMC4_OVF (RO, If PMC4 present)

PMC3_OVF (RO)

PMC2_OVF (RO)

PMC1_OVF (RO)

PMC0_OVF (RO)

Valid if CPUID.0AH:EAX[15:8] = 8; else reserved

Ovf_UncorePMU

61

62

FIXED_CTR2 ClrOverflow

FIXED_CTR1 ClrOverflow

FIXED_CTR0 ClrOverflow

PMC7_ClrOvf (if PMC7 present)

2 1 0

PMC6_ClrOvf (if PMC6 present)

31

32

33

34

35

Reserved

63

ClrCondChgd

ClrOvfDSBuffer

8 7 6 5 4 3

PMC5_ClrOvf (if PMC5 present)

PMC4_ClrOvf (if PMC4 present)

PMC3_ClrOvf

PMC2_ClrOvf

PMC1_ClrOvf

PMC0_ClrOvf

Valid if CPUID.0AH:EAX[15:8] = 8; else reserved

ClrOvfUncore