18-18 Vol. 3B

PERFORMANCE MONITORING

Writing 0 to both bits stops the performance counter. Writing 11B causes the counter to increment irrespective

of privilege levels.

•

PMI field (fourth bit in each 4-bit control) — When set, the logical processor generates an exception

through its local APIC on overflow condition of the respective fixed-function counter.

18.4.2

Global Counter Control Facilities

Processors based on Intel Core microarchitecture provides simplified performance counter control that simplifies

the most frequent operations in programming performance events, i.e. enabling/disabling event counting and

checking the status of counter overflows. This is done by the following three MSRs:

•

MSR_PERF_GLOBAL_CTRL enables/disables event counting for all or any combination of fixed-function PMCs

(MSR_PERF_FIXED_CTRx) or general-purpose PMCs via a single WRMSR.

•

MSR_PERF_GLOBAL_STATUS allows software to query counter overflow conditions on any combination of

fixed-function PMCs (MSR_PERF_FIXED_CTRx) or general-purpose PMCs via a single RDMSR.

•

MSR_PERF_GLOBAL_OVF_CTRL allows software to clear counter overflow conditions on any combination of

fixed-function PMCs (MSR_PERF_FIXED_CTRx) or general-purpose PMCs via a single WRMSR.

MSR_PERF_GLOBAL_CTRL MSR provides single-bit controls to enable counting in each performance counter (see

Figure 18-15). Each enable bit in MSR_PERF_GLOBAL_CTRL is AND’ed with the enable bits for all privilege levels in

the respective IA32_PERFEVTSELx or MSR_PERF_FIXED_CTR_CTRL MSRs to start/stop the counting of respective

counters. Counting is enabled if the AND’ed results is true; counting is disabled when the result is false.

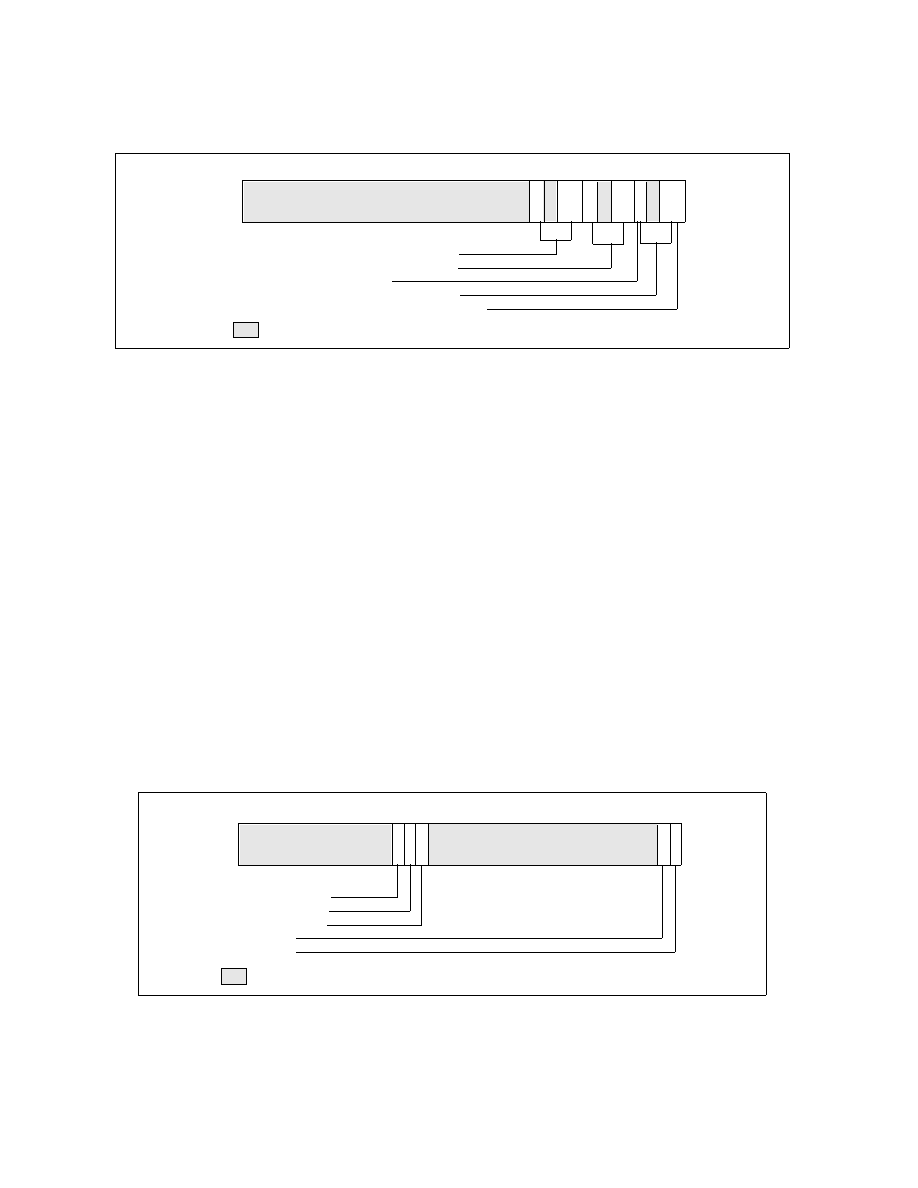

Figure 18-14. Layout of MSR_PERF_FIXED_CTR_CTRL MSR

Figure 18-15. Layout of MSR_PERF_GLOBAL_CTRL MSR

Cntr2 — Controls for MSR_PERF_FIXED_CTR2

Cntr1 — Controls for MSR_PERF_FIXED_CTR1

PMI — Enable PMI on overflow

Cntr0 — Controls for MSR_PERF_FIXED_CTR0

8 7

0

ENABLE — 0: disable; 1: OS; 2: User; 3: All ring levels

E

N

P

M

I

11

3

12

1

Reserved

63

2

E

N

E

N

4

9

5

P

P

M

M

I

I

FIXED_CTR2 enable

FIXED_CTR1 enable

FIXED_CTR0 enable

PMC1 enable

2 1 0

PMC0 enable

31

32

33

34

35

Reserved

63