Vol. 3B 16-13

INTERPRETING MACHINE-CHECK ERROR CODES

16.5

INCREMENTAL DECODING INFORMATION: PROCESSOR FAMILY WITH

CPUID DISPLAYFAMILY_DISPLAYMODEL SIGNATURE 06_3EH, MACHINE

ERROR CODES FOR MACHINE CHECK

Intel Xeon processor E5 v2 family and Intel Xeon processor E7 v2 family are based on the Ivy Bridge-EP microar-

chitecture and can be identified with CPUID DisplayFamily_DisplaySignature 06_3EH. Incremental error codes for

internal machine check error from PCU controller is reported in the register bank IA32_MC4, Table lists model-

specific fields to interpret error codes applicable to IA32_MC4_STATUS. Incremental MC error codes related to the

Intel QPI links are reported in the register banks IA32_MC5. Information listed in Table 16-14 for QPI MC error code

apply to IA32_MC5_STATUS. Incremental error codes for the memory controller unit is reported in the register

banks IA32_MC9-IA32_MC16. Table 16-18 lists model-specific error codes apply to IA32_MCi_STATUS, i = 9-16.

16.5.1 Internal Machine Check Errors

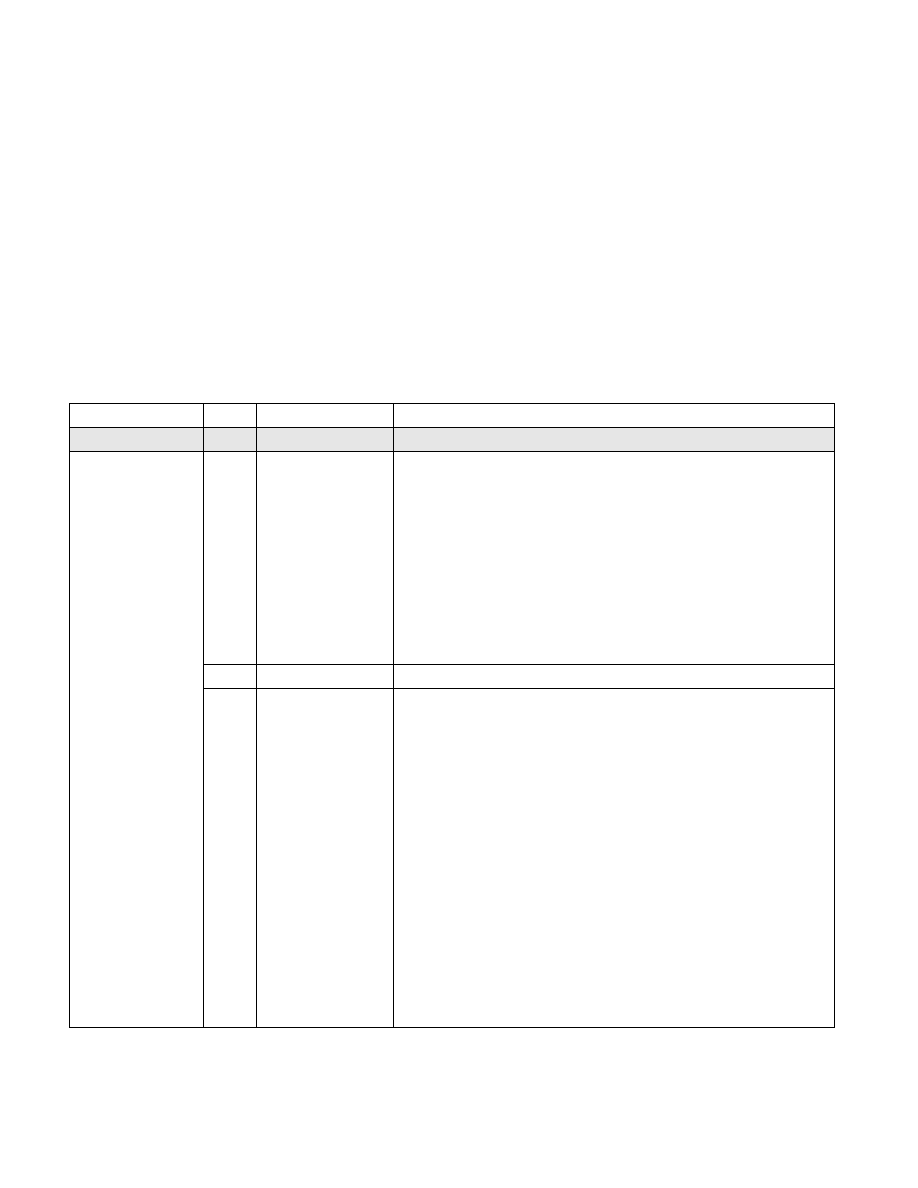

Table 16-17. Machine Check Error Codes for IA32_MC4_STATUS

Type

Bit No. Bit Function

Bit Description

MCA error codes

1

0-15

MCACOD

Model specific errors 19:16

Reserved except for

the following

0000b - No Error

0001b - Non_IMem_Sel

0010b - I_Parity_Error

0011b - Bad_OpCode

0100b - I_Stack_Underflow

0101b - I_Stack_Overflow

0110b - D_Stack_Underflow

0111b - D_Stack_Overflow

1000b - Non-DMem_Sel

1001b - D_Parity_Error

23-20

Reserved

Reserved

31-24

Reserved except for

the following

00h - No Error

0Dh - MC_IMC_FORCE_SR_S3_TIMEOUT

0Eh - MC_CPD_UNCPD_ST_TIMEOUT

0Fh - MC_PKGS_SAFE_WP_TIMEOUT

43h - MC_PECI_MAILBOX_QUIESCE_TIMEOUT

44h - MC_CRITICAL_VR_FAILED

45h - MC_ICC_MAX-NOTSUPPORTED

5Ch - MC_MORE_THAN_ONE_LT_AGENT

60h - MC_INVALID_PKGS_REQ_PCH

61h - MC_INVALID_PKGS_REQ_QPI

62h - MC_INVALID_PKGS_RES_QPI

63h - MC_INVALID_PKGC_RES_PCH

64h - MC_INVALID_PKG_STATE_CONFIG

70h - MC_WATCHDG_TIMEOUT_PKGC_SLAVE

71h - MC_WATCHDG_TIMEOUT_PKGC_MASTER

72h - MC_WATCHDG_TIMEOUT_PKGS_MASTER