Vol. 3B 16-11

INTERPRETING MACHINE-CHECK ERROR CODES

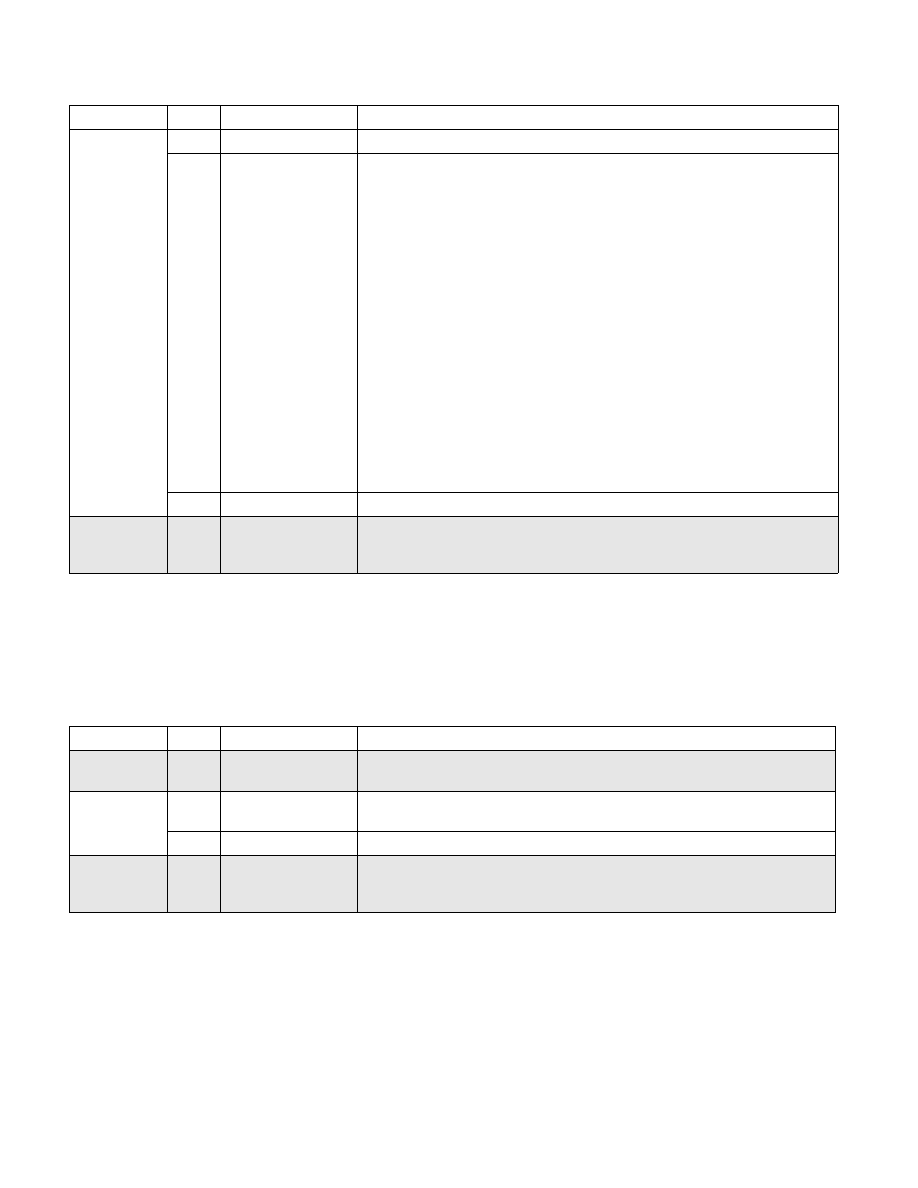

16.4.2 Intel QPI Machine Check Errors

Table 16-14. Intel QPI MC Error Codes for IA32_MC6_STATUS and IA32_MC7_STATUS

16.4.3 Integrated Memory Controller Machine Check Errors

MC error codes associated with integrated memory controllers are reported in the MSRs IA32_MC8_STATUS-

IA32_MC11_STATUS. The supported error codes are follows the architectural MCACOD definition type 1MMMCCCC

(see Chapter 15, “Machine-Check Architecture,”). MSR_ERROR_CONTROL.[bit 1] can enable additional informa-

23-20

Reserved

Reserved

31-24

Reserved except for

the following

00h - No Error

0Dh - MC_IMC_FORCE_SR_S3_TIMEOUT

0Eh - MC_CPD_UNCPD_ST_TIMEOUT

0Fh - MC_PKGS_SAFE_WP_TIMEOUT

43h - MC_PECI_MAILBOX_QUIESCE_TIMEOUT

5Ch - MC_MORE_THAN_ONE_LT_AGENT

60h - MC_INVALID_PKGS_REQ_PCH

61h - MC_INVALID_PKGS_REQ_QPI

62h - MC_INVALID_PKGS_RES_QPI

63h - MC_INVALID_PKGC_RES_PCH

64h - MC_INVALID_PKG_STATE_CONFIG

70h - MC_WATCHDG_TIMEOUT_PKGC_SLAVE

71h - MC_WATCHDG_TIMEOUT_PKGC_MASTER

72h - MC_WATCHDG_TIMEOUT_PKGS_MASTER

7ah - MC_HA_FAILSTS_CHANGE_DETECTED

81h - MC_RECOVERABLE_DIE_THERMAL_TOO_HOT

56-32

Reserved

Reserved

Status register

validity

indicators

1

57-63

NOTES:

1. These fields are architecturally defined. Refer to Chapter 15, “Machine-Check Architecture,” for more information.

Type

Bit No. Bit Function

Bit Description

MCA error

codes

1

NOTES:

1. These fields are architecturally defined. Refer to Chapter 15, “Machine-Check Architecture,” for more information.

0-15

MCACOD

Bus error format: 1PPTRRRRIILL

Model specific

errors

56-16

Reserved

Reserved

Status register

validity

indicators

1

57-63

Type

Bit No. Bit Function

Bit Description