14-4 Vol. 3B

POWER AND THERMAL MANAGEMENT

on default value of IA32_MISC_ENABLE[38] allows BIOS to detect the presence of hardware support of opportu-

nistic processor performance operation.

IA32_MISC_ENABLE[38] is shared across all logical processors in a physical package. It is written by BIOS during

platform initiation to enable/disable opportunistic processor operation in conjunction of OS power management

capabilities, see Section 14.3.2.2. BIOS can set IA32_MISC_ENABLE[38] with 1 to disable opportunistic processor

performance operation; it must clear the default value of IA32_MISC_ENABLE[38] to 0 to enable opportunistic

processor performance operation. OS and applications must use CPUID leaf 06H if it needs to detect processors

that has opportunistic processor operation enabled.

When CPUID is executed with EAX = 06H on input, Bit 1 of EAX in Leaf 06H (i.e. CPUID.06H:EAX[1]) indicates

opportunistic processor performance operation, such as IDA, has been enabled by BIOS.

Opportunistic processor performance operation can be disabled by setting bit 38 of IA32_MISC_ENABLE. This

mechanism is intended for BIOS only. If IA32_MISC_ENABLE[38] is set, CPUID.06H:EAX[1] will return 0.

14.3.2.2 OS Control of Opportunistic Processor Performance Operation

There may be phases of software execution in which system software cannot tolerate the non-deterministic aspects

of opportunistic processor performance operation. For example, when calibrating a real-time workload to make a

CPU reservation request to the OS, it may be undesirable to allow the possibility of the processor delivering

increased performance that cannot be sustained after the calibration phase.

System software can temporarily disengage opportunistic processor performance operation by setting bit 32 of the

IA32_PERF_CTL MSR (0199H), using a read-modify-write sequence on the MSR. The opportunistic processor

performance operation can be re-engaged by clearing bit 32 in IA32_PERF_CTL MSR, using a read-modify-write

sequence. The DISENAGE bit in IA32_PERF_CTL is not reflected in bit 32 of the IA32_PERF_STATUS MSR (0198H),

and it is not shared between logical processors in a physical package. In order for OS to engage IDA/Turbo mode,

the BIOS must

•

enable opportunistic processor performance operation, as described in Section 14.3.2.1,

•

expose the operating points associated with IDA/Turbo mode to the OS.

14.3.2.3 Required Changes to OS Power Management P-state Policy

Intel Dynamic Acceleration (IDA) and Intel Turbo Boost Technology can provide opportunistic performance greater

than the performance level corresponding to the Processor Base frequency of the processor (see CPUID’s processor

frequency information). System software can use a pair of MSRs to observe performance feedback. Software must

query for the presence of IA32_APERF and IA32_MPERF (see Section 14.2). The ratio between IA32_APERF and

IA32_MPERF is architecturally defined and a value greater than unity indicates performance increase occurred

during the observation period due to IDA. Without incorporating such performance feedback, the target P-state

evaluation algorithm can result in a non-optimal P-state target.

There are other scenarios under which OS power management may want to disable IDA, some of these are listed

below:

•

When engaging ACPI defined passive thermal management, it may be more effective to disable IDA for the

duration of passive thermal management.

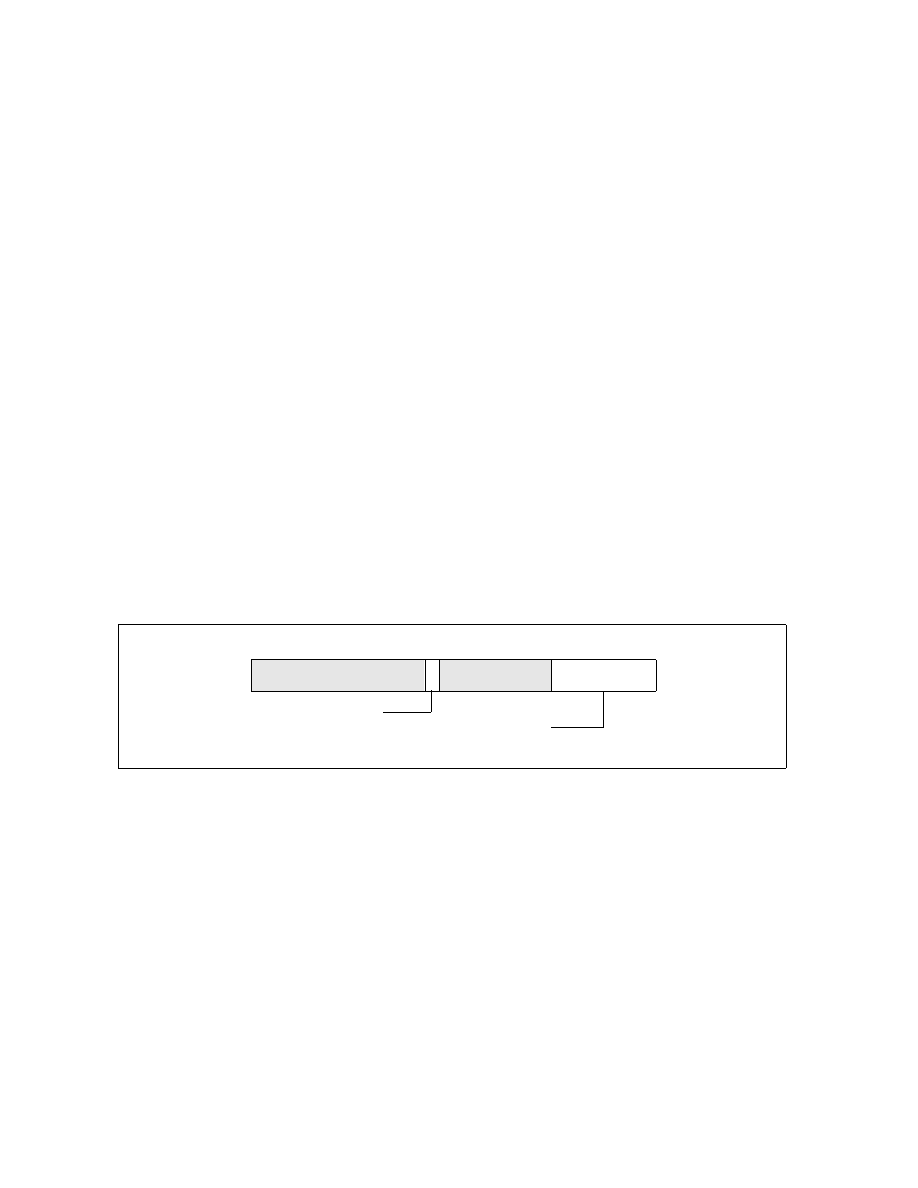

Figure 14-2. IA32_PERF_CTL Register

63

0

Reserved

16

Enhanced Intel Speedstep Technology Transition Target

15

32

33

31

IDA/Turbo DISENGAGE