Vol. 3A 13-3

SYSTEM PROGRAMMING FOR INSTRUCTION SET EXTENSIONS AND PROCESSOR EXTENDED STATES

2. Set CR4.OSXMMEXCPT[bit 10] = 1. Setting this flag implies that the operating system provides a SIMD

floating-point exception (#XM) handler (see Section 13.1.5, “Providing a Handler for the SIMD Floating-Point

Exception (#XM)”).

NOTE

The OSFXSR and OSXMMEXCPT bits in control register CR4 must be set by the operating system.

The processor has no other way of detecting operating-system support for the FXSAVE and

FXRSTOR instructions or for handling SIMD floating-point exceptions.

3. Clear CR0.EM[bit 2] = 0. This action disables emulation of the x87 FPU, which is required when executing SSE

instructions (see Section 2.5, “Control Registers”).

4. Set CR0.MP[bit 1] = 1. This setting is required for Intel 64 and IA-32 processors that support the SSE

extensions (see Section 9.2.1, “Configuring the x87 FPU Environment”).

Table 13-1 and Table 13-2 show the actions of the processor when an SSE instruction is executed, depending on

the following:

•

OSFXSR and OSXMMEXCPT flags in control register CR4

•

SSE/SSE2/SSE3/SSSE3/SSE4 feature flags returned by CPUID

•

EM, MP, and TS flags in control register CR0

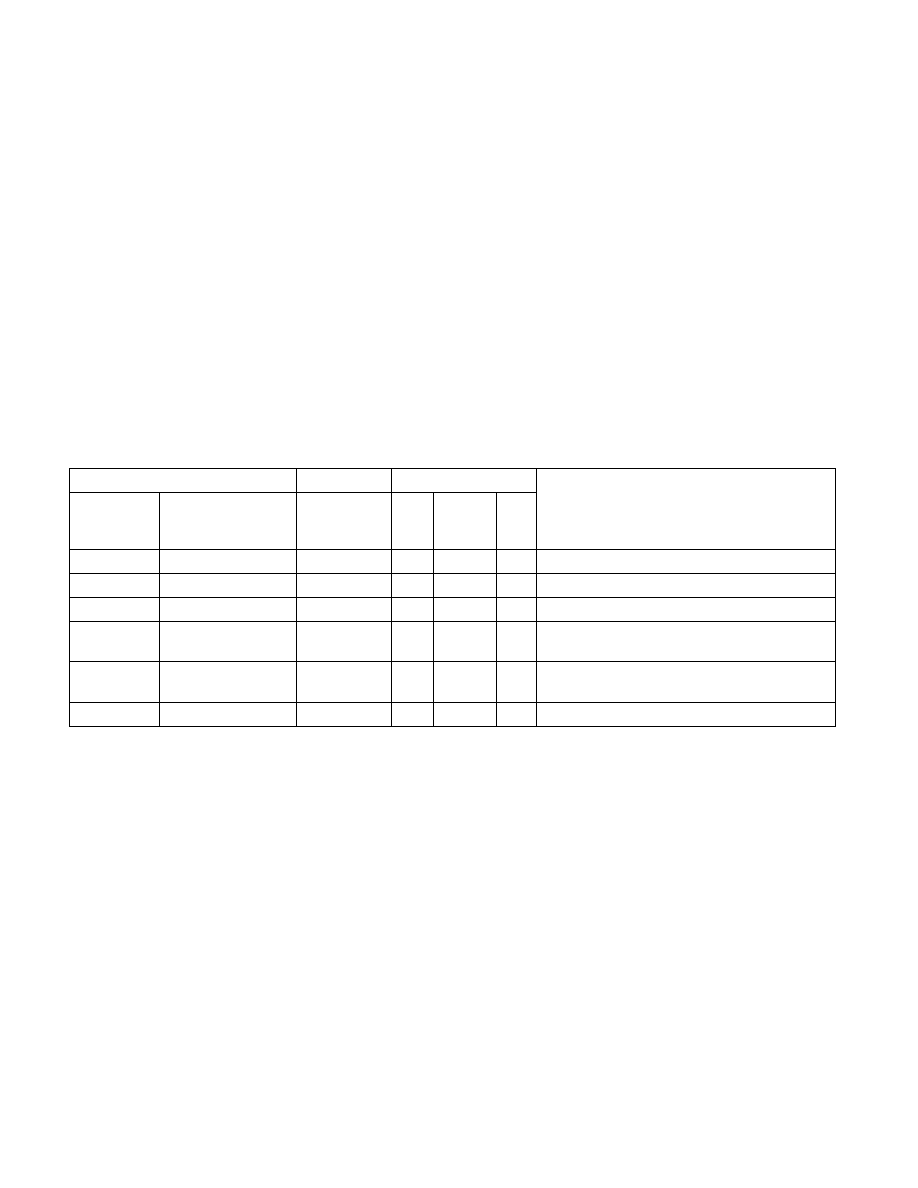

Table 13-1. Action Taken for Combinations of OSFXSR, OSXMMEXCPT, SSE, SSE2, SSE3, EM, MP, and TS

1

NOTES:

1. For execution of any SSE instruction except the PAUSE, PREFETCHh, SFENCE, LFENCE, MFENCE, MOVNTI, and CLFLUSH instructions.

CR4

CPUID

CR0 Flags

OSFXSR

OSXMMEXCPT

SSE, SSE2,

SSE3

2

,

SSE4_1

3

2. Exception conditions due to CR4.OSFXSR or CR4.OSXMMEXCPT do not apply to FISTTP.

3. Only applies to DPPS, DPPD, ROUNDPS, ROUNDPD, ROUNDSS, ROUNDSD.

EM

MP

4

4. For processors that support the MMX instructions, the MP flag should be set.

TS

Action

0

X

5

5. X = Don’t care.

X

X

1

X

#UD exception.

1

X

0

X

1

X

#UD exception.

1

X

1

1

1

X

#UD exception.

1

0

1

0

1

0

Execute instruction; #UD exception if unmasked

SIMD floating-point exception is detected.

1

1

1

0

1

0

Execute instruction; #XM exception if unmasked

SIMD floating-point exception is detected.

1

X

1

0

1

1

#NM exception.