11-24 Vol. 3A

MEMORY CACHE CONTROL

Figure 11-7 shows flags and fields in these registers. The functions of these flags and fields are:

•

Type field, bits 0 through 7 — Specifies the memory type for the range (see Table 11-8 for the encoding of

this field).

•

PhysBase field, bits 12 through (MAXPHYADDR-1) — Specifies the base address of the address range.

This 24-bit value, in the case where MAXPHYADDR is 36 bits, is extended by 12 bits at the low end to form the

base address (this automatically aligns the address on a 4-KByte boundary).

•

PhysMask field, bits 12 through (MAXPHYADDR-1) — Specifies a mask (24 bits if the maximum physical

address size is 36 bits, 28 bits if the maximum physical address size is 40 bits). The mask determines the range

of the region being mapped, according to the following relationships:

— Address_Within_Range AND PhysMask = PhysBase AND PhysMask

— This value is extended by 12 bits at the low end to form the mask value. For more information: see Section

11.11.3, “Example Base and Mask Calculations.”

— The width of the PhysMask field depends on the maximum physical address size supported by the

processor.

CPUID.80000008H reports the maximum physical address size supported by the processor. If

CPUID.80000008H is not available, software may assume that the processor supports a 36-bit physical

address size (then PhysMask is 24 bits wide and the upper 28 bits of IA32_MTRR_PHYSMASKn are

reserved). See the Note below.

•

V (valid) flag, bit 11 — Enables the register pair when set; disables register pair when clear.

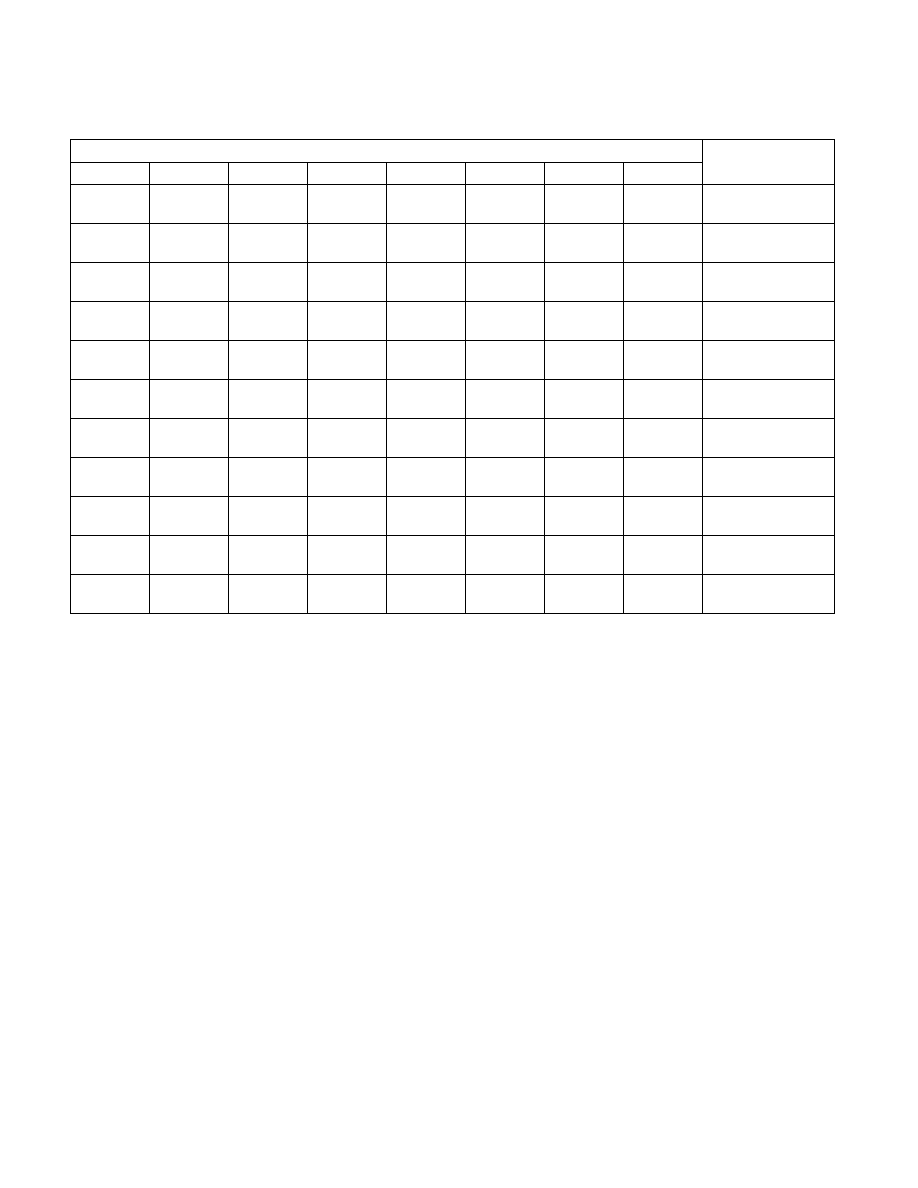

Table 11-9. Address Mapping for Fixed-Range MTRRs

Address Range (hexadecimal)

MTRR

63 56

55 48

47 40

39 32

31 24

23 16

15 8

7 0

70000-

7FFFF

60000-

6FFFF

50000-

5FFFF

40000-

4FFFF

30000-

3FFFF

20000-

2FFFF

10000-

1FFFF

00000-

0FFFF

IA32_MTRR_

FIX64K_00000

9C000

9FFFF

98000-

9BFFF

94000-

97FFF

90000-

93FFF

8C000-

8FFFF

88000-

8BFFF

84000-

87FFF

80000-

83FFF

IA32_MTRR_

FIX16K_80000

BC000

BFFFF

B8000-

BBFFF

B4000-

B7FFF

B0000-

B3FFF

AC000-

AFFFF

A8000-

ABFFF

A4000-

A7FFF

A0000-

A3FFF

IA32_MTRR_

FIX16K_A0000

C7000

C7FFF

C6000-

C6FFF

C5000-

C5FFF

C4000-

C4FFF

C3000-

C3FFF

C2000-

C2FFF

C1000-

C1FFF

C0000-

C0FFF

IA32_MTRR_

FIX4K_C0000

CF000

CFFFF

CE000-

CEFFF

CD000-

CDFFF

CC000-

CCFFF

CB000-

CBFFF

CA000-

CAFFF

C9000-

C9FFF

C8000-

C8FFF

IA32_MTRR_

FIX4K_C8000

D7000

D7FFF

D6000-

D6FFF

D5000-

D5FFF

D4000-

D4FFF

D3000-

D3FFF

D2000-

D2FFF

D1000-

D1FFF

D0000-

D0FFF

IA32_MTRR_

FIX4K_D0000

DF000

DFFFF

DE000-

DEFFF

DD000-

DDFFF

DC000-

DCFFF

DB000-

DBFFF

DA000-

DAFFF

D9000-

D9FFF

D8000-

D8FFF

IA32_MTRR_

FIX4K_D8000

E7000

E7FFF

E6000-

E6FFF

E5000-

E5FFF

E4000-

E4FFF

E3000-

E3FFF

E2000-

E2FFF

E1000-

E1FFF

E0000-

E0FFF

IA32_MTRR_

FIX4K_E0000

EF000

EFFFF

EE000-

EEFFF

ED000-

EDFFF

EC000-

ECFFF

EB000-

EBFFF

EA000-

EAFFF

E9000-

E9FFF

E8000-

E8FFF

IA32_MTRR_

FIX4K_E8000

F7000

F7FFF

F6000-

F6FFF

F5000-

F5FFF

F4000-

F4FFF

F3000-

F3FFF

F2000-

F2FFF

F1000-

F1FFF

F0000-

F0FFF

IA32_MTRR_

FIX4K_F0000

FF000

FFFFF

FE000-

FEFFF

FD000-

FDFFF

FC000-

FCFFF

FB000-

FBFFF

FA000-

FAFFF

F9000-

F9FFF

F8000-

F8FFF

IA32_MTRR_

FIX4K_F8000