Vol. 3A 10-21

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

ery mode is model specific. For Pentium 4 and Intel Xeon processors, when

this shorthand is used together with lowest priority delivery mode, the IPI

may be redirected back to the issuing processor.

Destination

Specifies the target processor or processors. This field is only used when the destination

shorthand field is set to 00B. If the destination mode is set to physical, then bits 56 through 59

contain the APIC ID of the target processor for Pentium and P6 family processors and bits 56

through 63 contain the APIC ID of the target processor the for Pentium 4 and Intel Xeon

processors. If the destination mode is set to logical, the interpretation of the 8-bit destination

field depends on the settings of the DFR and LDR registers of the local APICs in all the proces-

sors in the system (see Section 10.6.2, “Determining IPI Destination”).

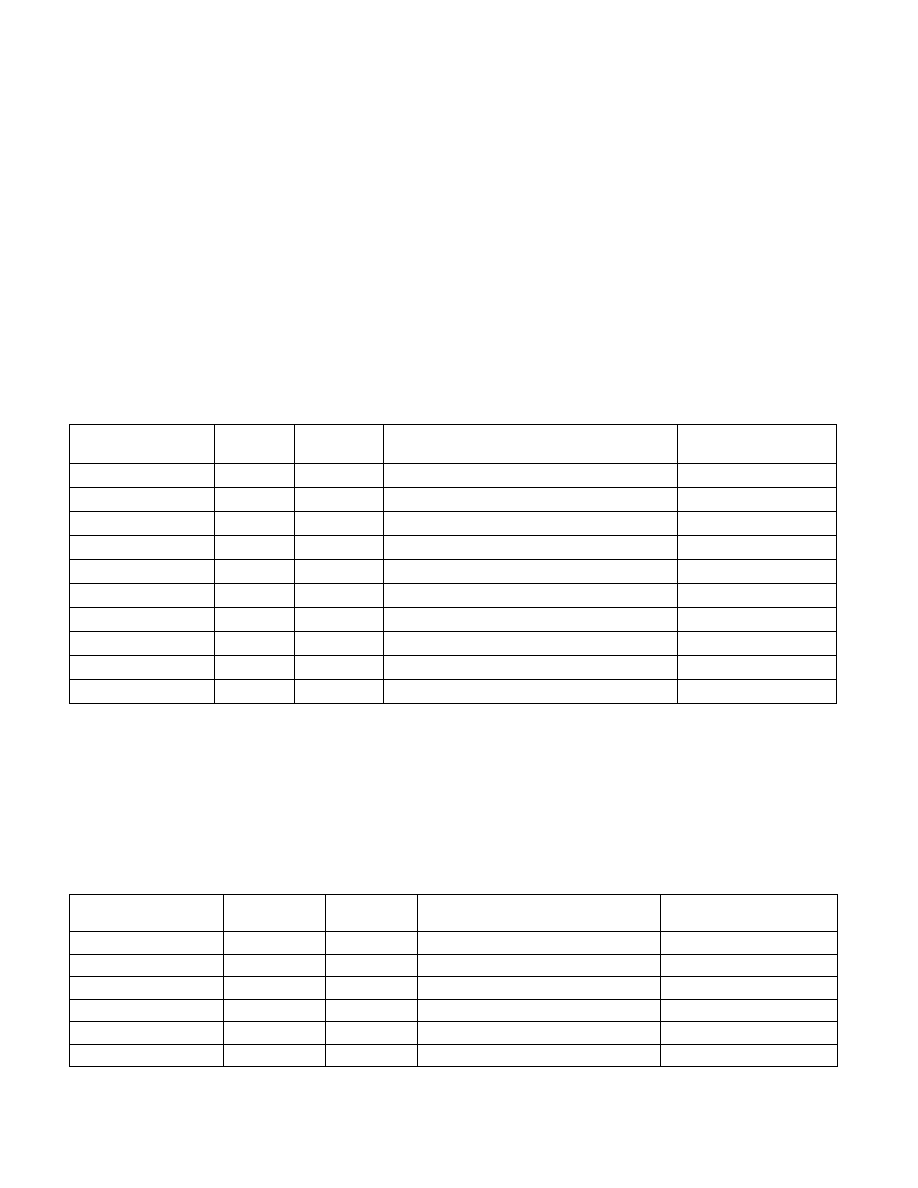

Not all combinations of options for the ICR are valid. Table 10-3 shows the valid combinations for the fields in the

ICR for the Pentium 4 and Intel Xeon processors; Table 10-4 shows the valid combinations for the fields in the ICR

for the P6 family processors. Also note that the lower half of the ICR may not be preserved over transitions to the

deepest C-States.

ICR operation in x2APIC mode is discussed in Section 10.12.9.

Table 10-3 Valid Combinations for the Pentium 4 and Intel Xeon Processors’

Local xAPIC Interrupt Command Register

Destination

Shorthand

Valid/

Invalid

Trigger

Mode

Delivery Mode

Destination Mode

No Shorthand

Valid

Edge

All Modes

1

Physical or Logical

No Shorthand

Invalid

2

Level

All Modes

Physical or Logical

Self

Valid

Edge

Fixed

X

3

Self

Invalid

2

Level

Fixed

X

Self

Invalid

X

Lowest Priority, NMI, INIT, SMI, Start-Up

X

All Including Self

Valid

Edge

Fixed

X

All Including Self

Invalid

2

Level

Fixed

X

All Including Self

Invalid

X

Lowest Priority, NMI, INIT, SMI, Start-Up

X

All Excluding Self

Valid

Edge

Fixed, Lowest Priority

1

,

4

, NMI, INIT, SMI, Start-Up

X

All Excluding Self

Invalid

2

Level

FIxed, Lowest Priority

4

, NMI, INIT, SMI, Start-Up

X

NOTES:

1. The ability of a processor to send a lowest priority IPI is model specific.

2. For these interrupts, if the trigger mode bit is 1 (Level), the local xAPIC will override the bit setting and issue the interrupt as an

edge triggered interrupt.

3. X means the setting is ignored.

4. When using the “lowest priority” delivery mode and the “all excluding self” destination, the IPI can be redirected back to the issuing

APIC, which is essentially the same as the “all including self” destination mode.

Table 10-4 Valid Combinations for the P6 Family Processors’

Local APIC Interrupt Command Register

Destination

Shorthand

Valid/

Invalid

Trigger Mode

Delivery Mode

Destination Mode

No Shorthand

Valid

Edge

All Modes

1

Physical or Logical

No Shorthand

Valid

2

Level

Fixed, Lowest Priority

1

, NMI

Physical or Logical

No Shorthand

Valid

3

Level

INIT

Physical or Logical

Self

Valid

Edge

Fixed

X

4

Self

1

Level

Fixed

X

Self

Invalid

5

X

Lowest Priority, NMI, INIT, SMI, Start-Up

X