10-44 Vol. 3A

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

•

If a BIOS transfers control to OS in xAPIC mode, then the BIOS must ensure that only logical processors with

CPUID.0BH.EDX value less than 255 are enabled. BIOS initialization on all logical processors with

CPUID.0B.EDX values greater than or equal to 255 must (a) disable APIC and execute CLI in each logical

processor, and (b) leave these logical processor in the lowest power state so that these processors do not

respond to INIT IPI during OS boot. The BSP and all the enabled logical processor operate in xAPIC mode after

BIOS passed control to OS. Application requiring processor topology information can use OS provided legacy

services based on 8-bit initial APIC IDs or legacy topology information from CPUID.01H and CPUID 04H leaves.

Even if the BIOS passes control in xAPIC mode, an OS can switch the processors to x2APIC mode later. BIOS

SMM handler should always read the APIC_BASE_MSR, determine the APIC mode and use the corresponding

access method.

10.12.9 ICR Operation in x2APIC Mode

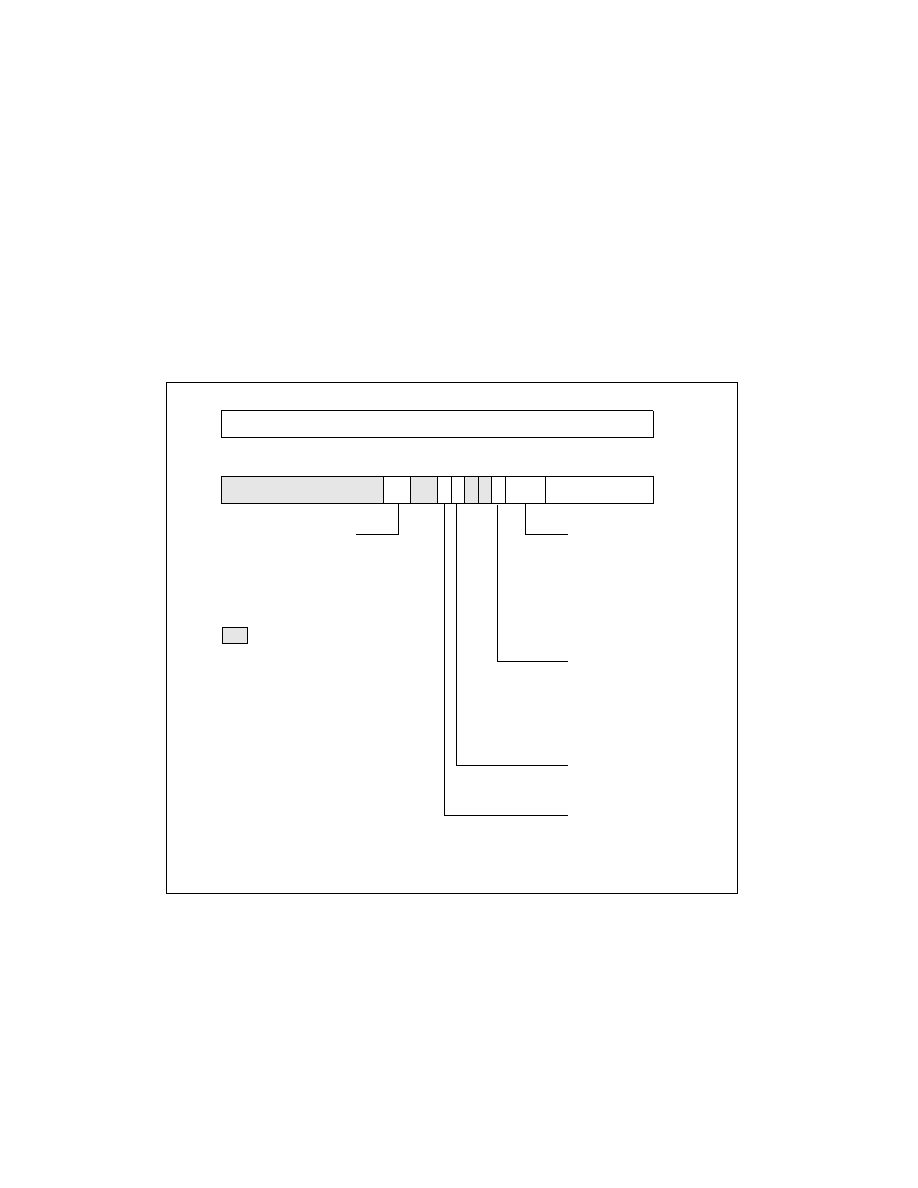

In x2APIC mode, the layout of the Interrupt Command Register is shown in Figure 10-12. The lower 32 bits of ICR

in x2APIC mode is identical to the lower half of the ICR in xAPIC mode, except the Delivery Status bit is removed

since it is not needed in x2APIC mode. The destination ID field is expanded to 32 bits in x2APIC mode.

To send an IPI using the ICR, software must set up the ICR to indicate the type of IPI message to be sent and the

destination processor or processors. Self IPIs can also be sent using the SELF IPI register (see Section 10.12.11).

A single MSR write to the Interrupt Command Register is required for dispatching an interrupt in x2APIC mode.

With the removal of the Delivery Status bit, system software no longer has a reason to read the ICR. It remains

readable only to aid in debugging; however, software should not assume the value returned by reading the ICR is

the last written value.

Figure 10-28. Interrupt Command Register (ICR) in x2APIC Mode

31

0

Reserved

7

Vector

Destination Shorthand

8

10

Delivery Mode

000: Fixed

001: Reserved

00: No Shorthand

01: Self

11

12

13

14

15

16

17

18

19

10: All Including Self

11: All Excluding Self

010: SMI

011: Reserved

100: NMI

101: INIT

110: Start Up

111: Reserved

Destination Mode

0: Physical

1: Logical

Level

0 = De-assert

1 = Assert

Trigger Mode

0: Edge

1: Level

63

32

Destination Field

Address: 830H (63 - 0)

Value after Reset: 0H

Reserved

20