Vol. 3A 10-17

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

process the initial-count register is set, counting will restart, using the new initial-count value. The initial-count

register is a read-write register; the current-count register is read only.

A write of 0 to the initial-count register effectively stops the local APIC timer, in both one-shot and periodic mode.

The LVT timer register determines the vector number that is delivered to the processor with the timer interrupt that

is generated when the timer count reaches zero. The mask flag in the LVT timer register can be used to mask the

timer interrupt.

10.5.4.1 TSC-Deadline Mode

The mode of operation of the local-APIC timer is determined by the LVT Timer Register. Specifically, if

CPUID.01H:ECX.TSC_Deadline[bit 24] = 0, the mode is determined by bit 17 of the register; if

CPUID.01H:ECX.TSC_Deadline[bit 24] = 1, the mode is determined by bits 18:17. See Figure 10-8. (If

CPUID.01H:ECX.TSC_Deadline[bit 24] = 0, bit 18 of the register is reserved.) A write to the LVT Timer Register

that changes the timer mode disarms the local APIC timer. The supported timer modes are given in Table 10-2. The

three modes of the local APIC timer are mutually exclusive.

TSC-deadline mode allows software to use the local APIC timer to signal an interrupt at an absolute time. In TSC-

deadline mode, writes to the initial-count register are ignored; and current-count register always reads 0. Instead,

timer behavior is controlled using the IA32_TSC_DEADLINE MSR.

The IA32_TSC_DEADLINE MSR (MSR address 6E0H) is a per-logical processor MSR that specifies the time at which

a timer interrupt should occur. Writing a non-zero 64-bit value into IA32_TSC_DEADLINE arms the timer. An inter-

rupt is generated when the logical processor’s time-stamp counter equals or exceeds the target value in the

IA32_TSC_DEADLINE MSR.

2

When the timer generates an interrupt, it disarms itself and clears the

IA32_TSC_DEADLINE MSR. Thus, each write to the IA32_TSC_DEADLINE MSR generates at most one timer inter-

rupt.

In TSC-deadline mode, writing 0 to the IA32_TSC_DEADLINE MSR disarms the local-APIC timer. Transitioning

between TSC-deadline mode and other timer modes also disarms the timer.

The hardware reset value of the IA32_TSC_DEADLINE MSR is 0. In other timer modes (LVT bit 18 = 0), the

IA32_TSC_DEADLINE MSR reads zero and writes are ignored.

Software can configure the TSC-deadline timer to deliver a single interrupt using the following algorithm:

1. Detect support for TSC-deadline mode by verifying CPUID.1:ECX.24 = 1.

2. Select the TSC-deadline mode by programming bits 18:17 of the LVT Timer register with 10b.

3. Program the IA32_TSC_DEADLINE MSR with the target TSC value at which the timer interrupt is desired. This

causes the processor to arm the timer.

4. The processor generates a timer interrupt when the value of time-stamp counter is greater than or equal to

that of IA32_TSC_DEADLINE. It then disarms the timer and clear the IA32_TSC_DEADLINE MSR. (Both the

time-stamp counter and the IA32_TSC_DEADLINE MSR are 64-bit unsigned integers.)

5. Software can re-arm the timer by repeating step 3.

The following are usage guidelines for TSC-deadline mode:

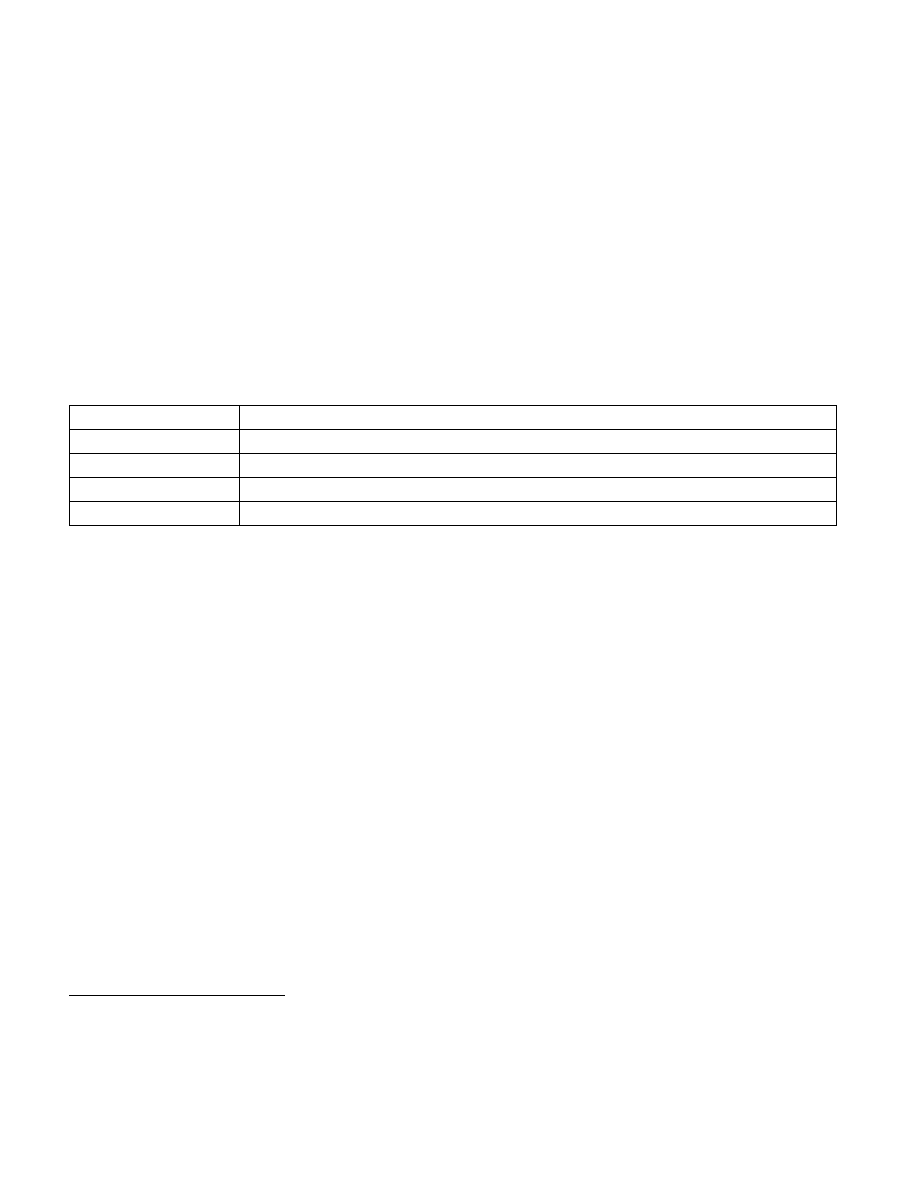

Table 10-2. Local APIC Timer Modes

LVT Bits [18:17]

Timer Mode

00b

One-shot mode, program count-down value in an initial-count register. See Section 10.5.4

01b

Periodic mode, program interval value in an initial-count register. See Section 10.5.4

10b

TSC-Deadline mode, program target value in IA32_TSC_DEADLINE MSR.

11b

Reserved

2. If the logical processor is in VMX non-root operation, a read of the time-stamp counter (using either RDMSR, RDTSC, or RDTSCP) may

not return the actual value of the time-stamp counter; see Chapter 27 of the Intel® 64 and IA-32 Architectures Software Devel-

oper’s Manual, Volume 3C. It is the responsibility of software operating in VMX root operation to coordinate the virtualization of the

time-stamp counter and the IA32_TSC_DEADLINE MSR.