Vol. 3A 9-7

PROCESSOR MANAGEMENT AND INITIALIZATION

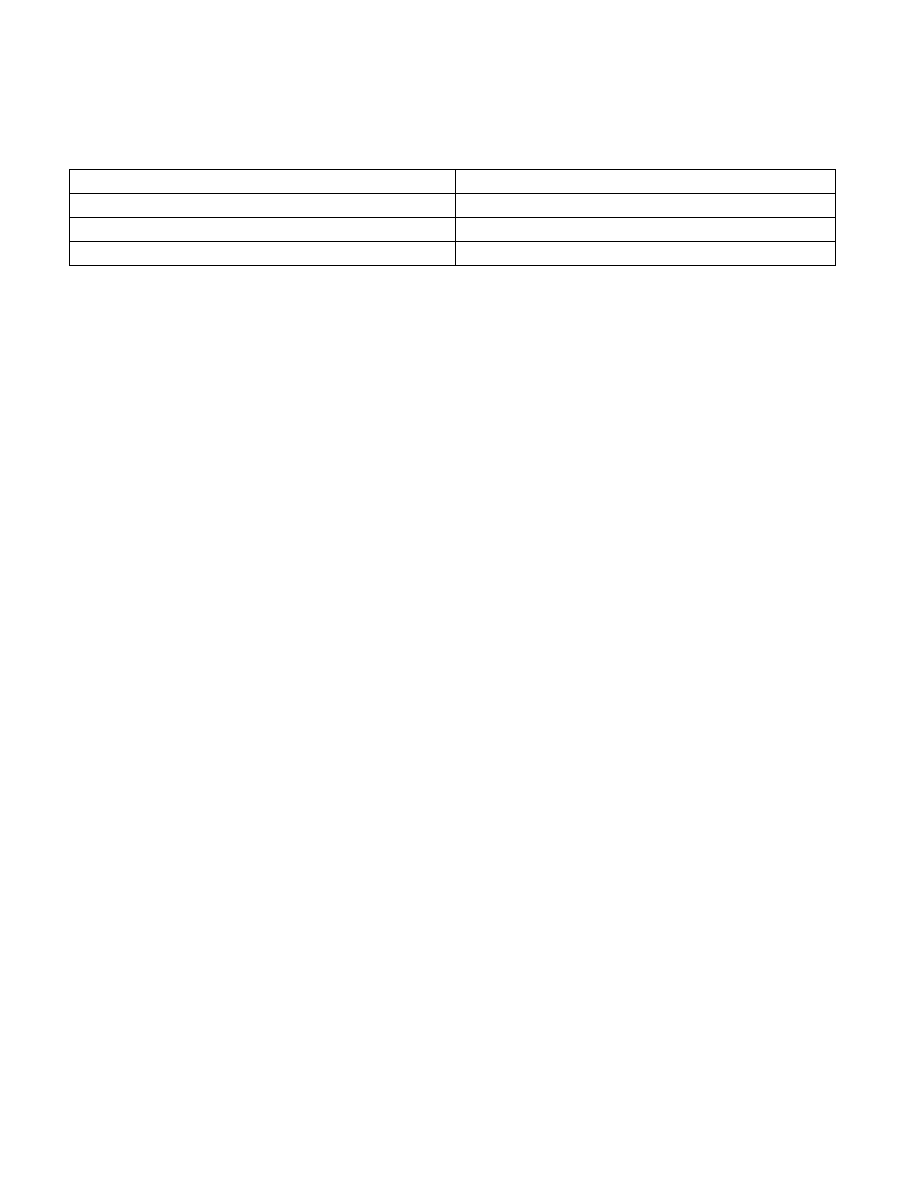

To emulate floating-point instructions, the EM, MP, and NE flag in control register CR0 should be set as shown in

Table 9-4.

Regardless of the value of the EM bit, the Intel486 SX processor generates a device-not-available exception (#NM)

upon encountering any floating-point instruction.

9.3 CACHE

ENABLING

IA-32 processors (beginning with the Intel486 processor) and Intel 64 processors contain internal instruction and

data caches. These caches are enabled by clearing the CD and NW flags in control register CR0. (They are set

during a hardware reset.) Because all internal cache lines are invalid following reset initialization, it is not neces-

sary to invalidate the cache before enabling caching. Any external caches may require initialization and invalidation

using a system-specific initialization and invalidation code sequence.

Depending on the hardware and operating system or executive requirements, additional configuration of the

processor’s caching facilities will probably be required. Beginning with the Intel486 processor, page-level caching

can be controlled with the PCD and PWT flags in page-directory and page-table entries. Beginning with the P6

family processors, the memory type range registers (MTRRs) control the caching characteristics of the regions of

physical memory. (For the Intel486 and Pentium processors, external hardware can be used to control the caching

characteristics of regions of physical memory.) See Chapter 11, “Memory Cache Control,” for detailed information

on configuration of the caching facilities in the Pentium 4, Intel Xeon, and P6 family processors and system

memory.

9.4

MODEL-SPECIFIC REGISTERS (MSRS)

Most IA-32 processors (starting from Pentium processors) and Intel 64 processors contain a model-specific regis-

ters (MSRs). A given MSR may not be supported across all families and models for Intel 64 and IA-32 processors.

Some MSRs are designated as architectural to simplify software programming; a feature introduced by an architec-

tural MSR is expected to be supported in future processors. Non-architectural MSRs are not guaranteed to be

supported or to have the same functions on future processors.

MSRs that provide control for a number of hardware and software-related features, include:

•

Performance-monitoring counters (see Chapter 23, “Introduction to Virtual Machine Extensions”).

•

Debug extensions (see Chapter 23, “Introduction to Virtual Machine Extensions.”).

•

Machine-check exception capability and its accompanying machine-check architecture (see Chapter 15,

“Machine-Check Architecture”).

•

MTRRs (see Section 11.11, “Memory Type Range Registers (MTRRs)”).

•

Thermal and power management.

•

Instruction-specific support (for example: SYSENTER, SYSEXIT, SWAPGS, etc.).

•

Processor feature/mode support (for example: IA32_EFER, IA32_FEATURE_CONTROL).

The MSRs can be read and written to using the RDMSR and WRMSR instructions, respectively.

When performing software initialization of an IA-32 or Intel 64 processor, many of the MSRs will need to be initial-

ized to set up things like performance-monitoring events, run-time machine checks, and memory types for phys-

ical memory.

Table 9-4. Software Emulation Settings of EM, MP, and NE Flags

CR0 Bit

Value

EM

1

MP

0

NE

1