8-26 Vol. 3A

MULTIPLE-PROCESSOR MANAGEMENT

8.6.3

Executing Multiple Threads on an Intel

®

64 or IA-32 Processor Supporting Hardware

Multi-Threading

Upon completing the operating system boot-up procedure, the bootstrap processor (BSP) executes operating

system code. Other logical processors are placed in the halt state. To execute a code stream (thread) on a halted

logical processor, the operating system issues an interprocessor interrupt (IPI) addressed to the halted logical

processor. In response to the IPI, the processor wakes up and begins executing the code identified by the vector

received as part of the IPI.

To manage execution of multiple threads on logical processors, an operating system can use conventional

symmetric multiprocessing (SMP) techniques. For example, the operating-system can use a time-slice or load

balancing mechanism to periodically interrupt each of the active logical processors. Upon interrupting a logical

processor, the operating system checks its run queue for a thread waiting to be executed and dispatches the thread

to the interrupted logical processor.

8.6.4

Handling Interrupts on an IA-32 Processor Supporting Hardware Multi-Threading

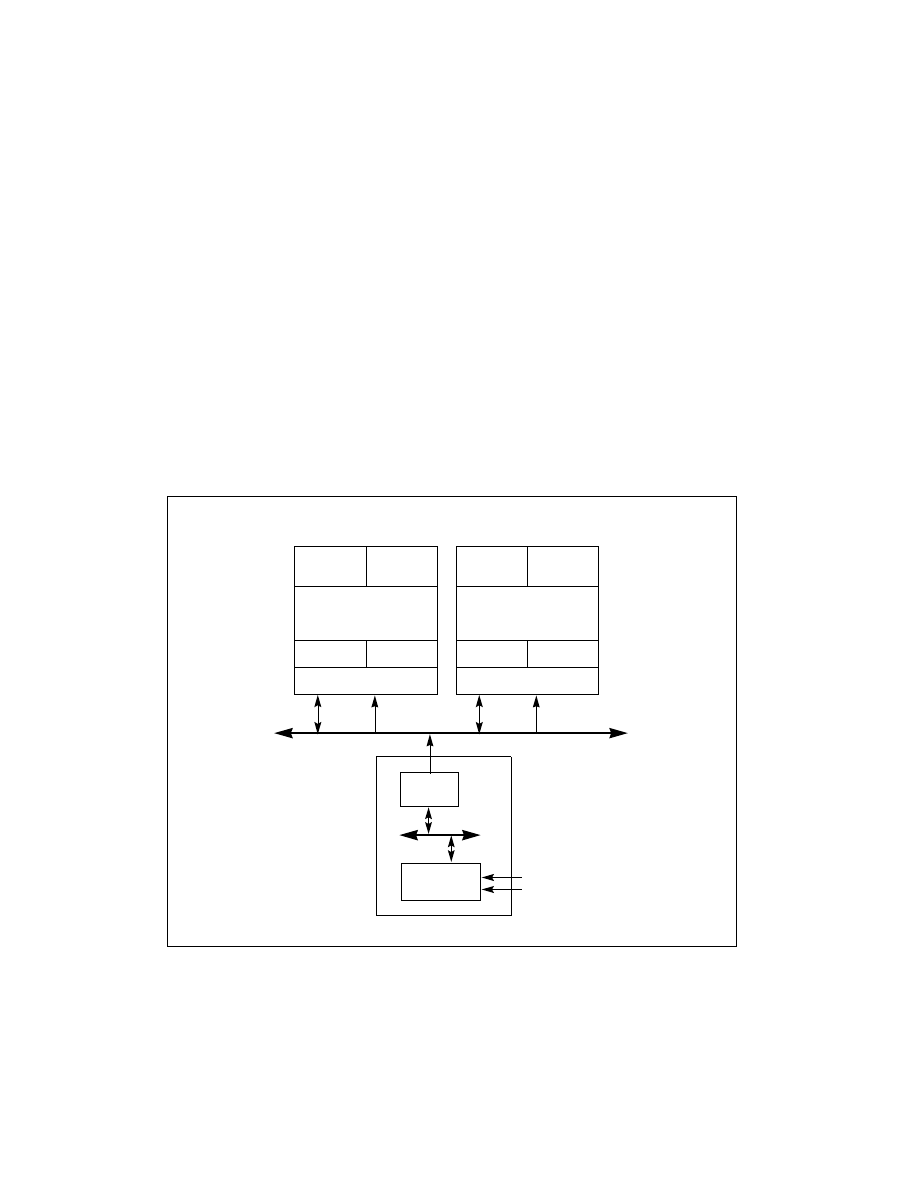

Interrupts are handled on processors supporting Intel Hyper-Threading Technology as they are on conventional MP

systems. External interrupts are received by the I/O APIC, which distributes them as interrupt messages to specific

logical processors (see Figure 8-3).

Logical processors can also send IPIs to other logical processors by writing to the ICR register of its local APIC (see

Section 10.6, “Issuing Interprocessor Interrupts”). This also applies to dual-core processors.

8.7 INTEL

®

HYPER-THREADING TECHNOLOGY ARCHITECTURE

Figure 8-4 shows a generalized view of an Intel processor supporting Intel Hyper-Threading Technology, using the

original Intel Xeon processor MP as an example. This implementation of the Intel Hyper-Threading Technology

Figure 8-3. Local APICs and I/O APIC in MP System Supporting Intel HT Technology

I/O APIC

External

Interrupts

System Chip Set

Bridge

PCI

Interrupt Messages

Local APIC

Logical

Processor 0

Local APIC

Logical

Processor 1

Hyper-Threading Technology

Intel Processor with Intel

Bus Interface

Processor Core

IPIs

Interrupt

Messages

Local APIC

Logical

Processor 0

Local APIC

Logical

Processor 1

Hyper-Threading Technology

Intel Processor with Intel

Bus Interface

Processor Core

IPIs

Interrupt

Messages