36-16 Vol. 3C

INTEL® PROCESSOR TRACE

Note: Software may write the same value back to IA32_RTIT_CTL without #GP, even if TraceEn=1.

•

All configuration MSRs for Intel PT are duplicated per logical processor

•

For each configuration MSR, any MSR write that attempts to change bits marked reserved, or utilize encodings

marked reserved, will cause a #GP fault.

•

All configuration MSRs for Intel PT are cleared on a cold RESET.

— If CPUID.(EAX=14H, ECX=0):EBX.IPFILT_WRSTPRSV[bit 2] = 1, only the TraceEn bit is cleared on warm

RESET; though this may have the impact of clearing other bits in IA32_RTIT_STATUS. Other MSR values of

the trace configuration MSRs are preserved on warm RESET.

•

The semantics of MSR writes to trace configuration MSRs in this chapter generally apply to explicit WRMSR to

these registers, using VM-exit or VM-entry MSR load list to these MSRs, XRSTORS with requested feature bit

map including XSAVE map component of state_8 (corresponding to IA32_XSS[bit 8]), and the write to

IA32_RTIT_CTL.TraceEn by XSAVES (Section 36.3.5.2).

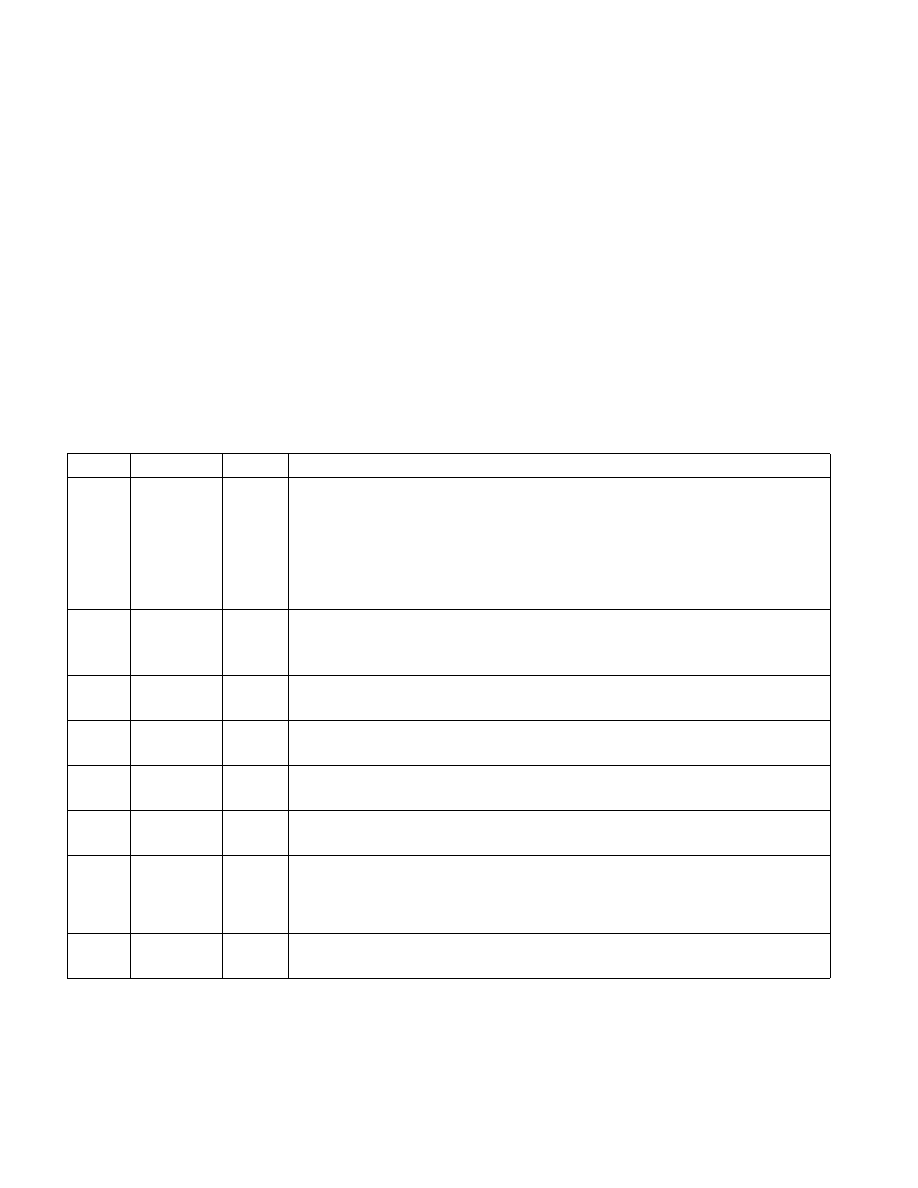

36.2.7.2 IA32_RTIT_CTL MSR

IA32_RTIT_CTL, at address 570H, is the primary enable and control MSR for trace packet generation. Bit positions

are listed in Table 36-6.

Table 36-6. IA32_RTIT_CTL MSR

Position

Bit Name

At Reset

Bit Description

0

TraceEn

0

If 1, enables tracing; else tracing is disabled if 0.

When this bit transitions from 1 to 0, all buffered packets are flushed out of internal buffers.

A further store, fence, or architecturally serializing instruction may be required to ensure that

packet data can be observed at the trace endpoint. See Section 36.2.7.3 for details of

enabling and disabling packet generation.

Note that the processor will clear this bit on #SMI (Section ) and warm reset. Other MSR bits

of IA32_RTIT_CTL (and other trace configuration MSRs) are not impacted by these events.

1

CYCEn

0

0: Disables CYC Packet (see Section 36.4.2.14).

1: Enables CYC Packet.

This bit is reserved if CPUID.(EAX=14H, ECX=0):EBX.CPSB_CAM[bit 1] = 0.

2

OS

0

0: Packet generation is disabled when CPL = 0.

1: Packet generation may be enabled when CPL = 0.

3

User

0

0: Packet generation is disabled when CPL > 0.

1: Packet generation may be enabled when CPL > 0.

4

PwrEvtEn

0

0: Power Event Trace packets are disabled.

1: Power Event Trace packets are enabled (see Section 36.2.3, “Power Event Tracing”).

5

FUPonPTW

0

0: PTW packets are not followed by FUPs.

1: PTW packets are followed by FUPs.

6

FabricEn

0

0: Trace output is directed to the memory subsystem, mechanism depends on

IA32_RTIT_CTL.ToPA.

1: Trace output is directed to the trace transport subsystem, IA32_RTIT_CTL.ToPA is ignored.

This bit is reserved if CPUID.(EAX=14H, ECX=0):ECX[bit 3] = 0.

7

CR3Filter

0

0: Disables CR3 filtering.

1: Enables CR3 filtering.