Vol. 3C 36-19

INTEL® PROCESSOR TRACE

36.2.7.3 Enabling and Disabling Packet Generation with TraceEn

When TraceEn transitions from 0 to 1, Intel Processor Trace is enabled, and a series of packets may be generated.

These packets help ensure that the decoder is aware of the state of the processor when the trace begins, and that

it can keep track of any timing or state changes that may have occurred while packet generation was disabled. A

full PSB+ (see Section 36.4.2.17) will be generated if IA32_RTIT_STATUS.PacketByteCnt=0, and may be gener-

ated in other cases as well. Otherwise, timing packets will be generated, including TSC, TMA, and CBR (see Section

36.4.2).

In addition to the packets discussed above, if and when PacketEn (Section 36.2.5.1) transitions from 0 to 1 (which

may happen immediately, depending on filtering settings), a TIP.PGE packet (Section 36.4.2.3) will be generated.

When TraceEn is set, the processor may read ToPA entries from memory and cache them internally. For this reason,

software should disable packet generation before making modifications to the ToPA tables (or changing the config-

uration of restricted memory regions). See Section 36.7 for more details of packets that may be generated with

modifications to TraceEn.

Disabling Packet Generation

Clearing TraceEn causes any packet data buffered within the logical processor to be flushed out, after which the

output MSRs (IA32_RTIT_OUTPUT_BASE and IA32_RTIT_OUTPUT_MASK_PTRS) will have stable values. When

output is directed to memory, a store, fence, or architecturally serializing instruction may be required to ensure

that the packet data is globally observed. No special packets are generated by disabling packet generation, though

a TIP.PGD may result if PacketEn=1 at the time of disable.

Other Writes to IA32_RTIT_CTL

Any attempt to modify IA32_RTIT_CTL while TraceEn is set will result in a general-protection fault (#GP) unless the

same write also clears TraceEn. However, writes to IA32_RTIT_CTL that do not modify any bits will not cause a

#GP, even if TraceEn remains set.

36.2.7.4 IA32_RTIT_STATUS MSR

The IA32_RTIT_STATUS MSR is readable and writable by software, but some bits (ContextEn, TriggerEn) are read-

only and cannot be directly modified. The WRMSR instruction ignores these bits in the source operand (attempts to

modify these bits are ignored and do not cause WRMSR to fault).

This MSR can only be written when IA32_RTIT_CTL.TraceEn is 0; otherwise WRMSR causes a general-protection

fault (#GP). The processor does not modify the value of this MSR while TraceEn is 0 (software can modify it with

WRMSR).

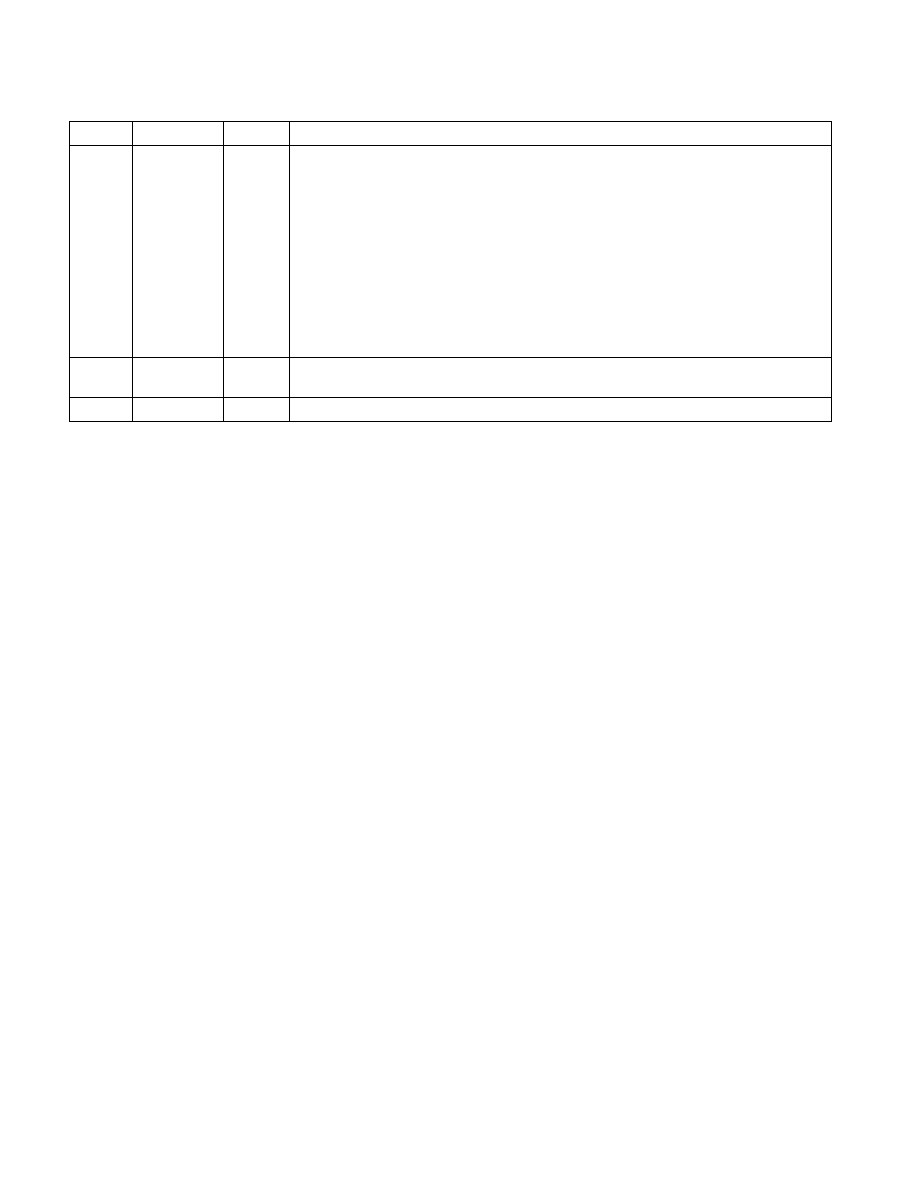

47:44

ADDR3_CFG

0

Configures the base/limit register pair IA32_RTIT_ADDR3_A/B based on the following

encodings:

0: ADDR3 range unused.

1: The [IA32_RTIT_ADDR3_A..IA32_RTIT_ADDR3_B] range defines a FilterEn range. FilterEn

will only be set when the IP is within this range, though other FilterEn ranges can additionally

be used. See Section 36.2.4.3 for details on IP filtering.

2: The [IA32_RTIT_ADDR3_A..IA32_RTIT_ADDR3_B] range defines a TraceStop range.

TraceStop will be asserted if code branches into this range. See Section 36.4.2.10 for details

on TraceStop.

3..15: Reserved (#GP).

This field is reserved if CPUID.(EAX=14H, ECX=1):EBX.RANGECNT[2:0] < 4.

59:48

Reserved

0

Reserved only for future trace content enables, or address filtering configuration enables.

Must be 0.

63:60

Reserved

0

Must be 0.

Table 36-6. IA32_RTIT_CTL MSR (Contd.)

Position

Bit Name

At Reset

Bit Description