36-6 Vol. 3C

INTEL® PROCESSOR TRACE

Note that some packets, such as MTC (Section 36.3.7) and other timing packets, do not depend on FilterEn. For

details on which packets depend on FilterEn, and hence are impacted by IP filtering, see Section 36.4.1.

TraceStop

The ADDRn ranges can also be configured to cause tracing to be disabled upon entry to the specified region. This is

intended for cases where unexpected code is executed, and the user wishes to immediately stop generating

packets in order to avoid overwriting previously written packets.

The TraceStop mechanism works much the same way that IP filtering does, and uses the same address comparison

logic. The TraceStop region base and limit values are programmed into one or more ADDRn ranges, but

IA32_RTIT_CTL.ADDRn_CFG is configured with the TraceStop encoding. Like FilterEn, TraceStop is detected when

a taken branch or event lands in a TraceStop region.

Further, TraceStop requires that TriggerEn=1 at the beginning of the branch/event, and ContextEn=1 upon

completion of the branch/event. When this happens, the CPU will set IA32_RTIT_STATUS.Stopped, thereby

clearing TriggerEn and hence disabling packet generation. This may generate a TIP.PGD packet with the target IP

of the branch or event that entered the TraceStop region. Finally, a TraceStop packet will be inserted, to indicate

that the condition was hit.

If a TraceStop condition is encountered during buffer overflow (Section 36.3.8), it will not be dropped, but will

instead be signaled once the overflow has resolved.

Note that a TraceStop event does not guarantee that all internally buffered packets are flushed out of internal

buffers. To ensure that this has occurred, the user should clear TraceEn.

To resume tracing after a TraceStop event, the user must first disable Intel PT by clearing IA32_RTIT_CTL.TraceEn

before the IA32_RTIT_STATUS.Stopped bit can be cleared. At this point Intel PT can be reconfigured, and tracing

resumed.

Note that the IA32_RTIT_STATUS.Stopped bit can also be set using the ToPA STOP bit. See Section 36.2.6.2.

IP Filtering Example

The following table gives an example of IP filtering behavior. Assume that IA32_RTIT_ADDRn_A = the IP of Range-

Base, and that IA32_RTIT_ADDRn_B = the IP of RangeLimit, while IA32_RTIT_CTL.ADDRn_CFG = 0x1 (enable

ADDRn range as a FilterEn range).

IP Filtering and TraceStop

It is possible for the user to configure IP filter range(s) and TraceStop range(s) that overlap. In this case, code

executing in the non-overlapping portion of either range will behave as would be expected from that range. Code

executing in the overlapping range will get TraceStop behavior.

36.2.5

Packet Generation Enable Controls

Intel Processor Trace includes a variety of controls that determine whether a packet is generated. In general, most

packets are sent only if Packet Enable (PacketEn) is set. PacketEn is an internal state maintained in hardware in

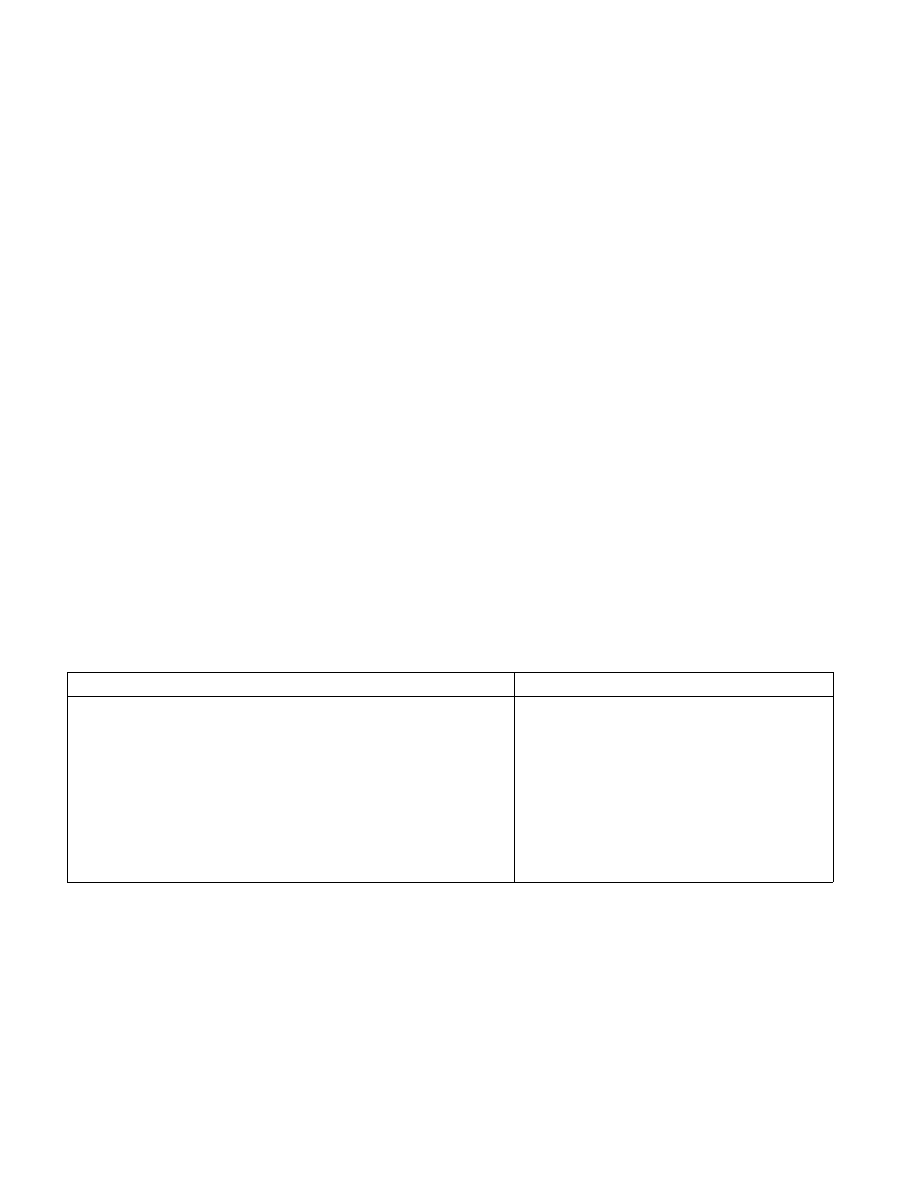

Table 36-2. IP Filtering Packet Example

Code Flow

Packets

Bar:

jmp RangeBase // jump into filter range

RangeBase:

jcc Foo // not taken

add eax, 1

Foo:

jmp RangeLimit+1 // jump out of filter range

RangeLimit:

nop

jcc Bar

TIP.PGE(RangeBase)

TNT(0)

TIP.PGD(RangeLimit+1)