Vol. 3C 36-33

INTEL® PROCESSOR TRACE

36.3.6.3 Cycle Thresholds

Software can opt to reduce the frequency of cycle packets, a trade-off to save bandwidth and intrusion at the

expense of precision. This is done by utilizing a cycle threshold (see Section 36.2.7.2).

IA32_RTIT_CTL.CycThresh indicates to the processor the minimum number of cycles that must pass before the

next CYC packet should be sent. If this value is 0, no threshold is used, and CYC packets can be sent every cycle in

which a CYC-eligible packet is generated. If this value is greater than 0, the hardware will wait until the associated

number of cycles have passed since the last CYC packet before sending another. CPUID provides the threshold

options for CycThresh, see Section 36.3.1.

Note that the cycle threshold does not dictate how frequently a CYC packet will be posted, it merely assigns the

maximum frequency. If the cycle threshold is 16, a CYC packet can be posted no more frequently than every 16

cycles. However, once that threshold of 16 cycles has passed, it still requires a new CYC-eligible packet to be gener-

ated before a CYC will be inserted. Table 36-14 illustrates the threshold behavior.

36.3.7

Decoder Synchronization (PSB+)

The PSB packet (Section 36.4.2.17) serves as a synchronization point for a trace-packet decoder. It is a pattern in

the trace log for which the decoder can quickly scan to align packet boundaries. No legal packet combination can

result in such a byte sequence. As such, it serves as the starting point for packet decode. To decode a trace log

properly, the decoder needs more than simply to be aligned: it needs to know some state and potentially some

timing information as well. The decoder should never need to retain any information (e.g., LastIP, call stack,

compound packet event) across a PSB; all compound packet events will be completed before a PSB, and any

compression state will be reset.

When a PSB packet is generated, it is followed by a PSBEND packet (Section 36.4.2.18). One or more packets may

be generated in between those two packets, and these inform the decoder of the current state of the processor.

These packets, known collectively as PSB+, should be interpreted as “status only”, since they do not imply any

change of state at the time of the PSB, nor are they associated directly with any instruction or event. Thus, the

Example 36-2. An Example of CYC in the Presence of Multi-Packet Operations

Time (cycles)

Instruction Snapshot

Generated Packets

x

jnz Foo (not taken)

CYC(?),

x + 2

ret (compressed)

x + 8

jnz Bar (taken)

x + 9

jmp %eax

TNT, CYC(9), TIP

x + 12

jnz Bar (not taken)

CYC(3)

x + 32

int3 (task gate)

TNT, FUP, CYC(10), PIP, CYC(20), MODE.Exec, TIP

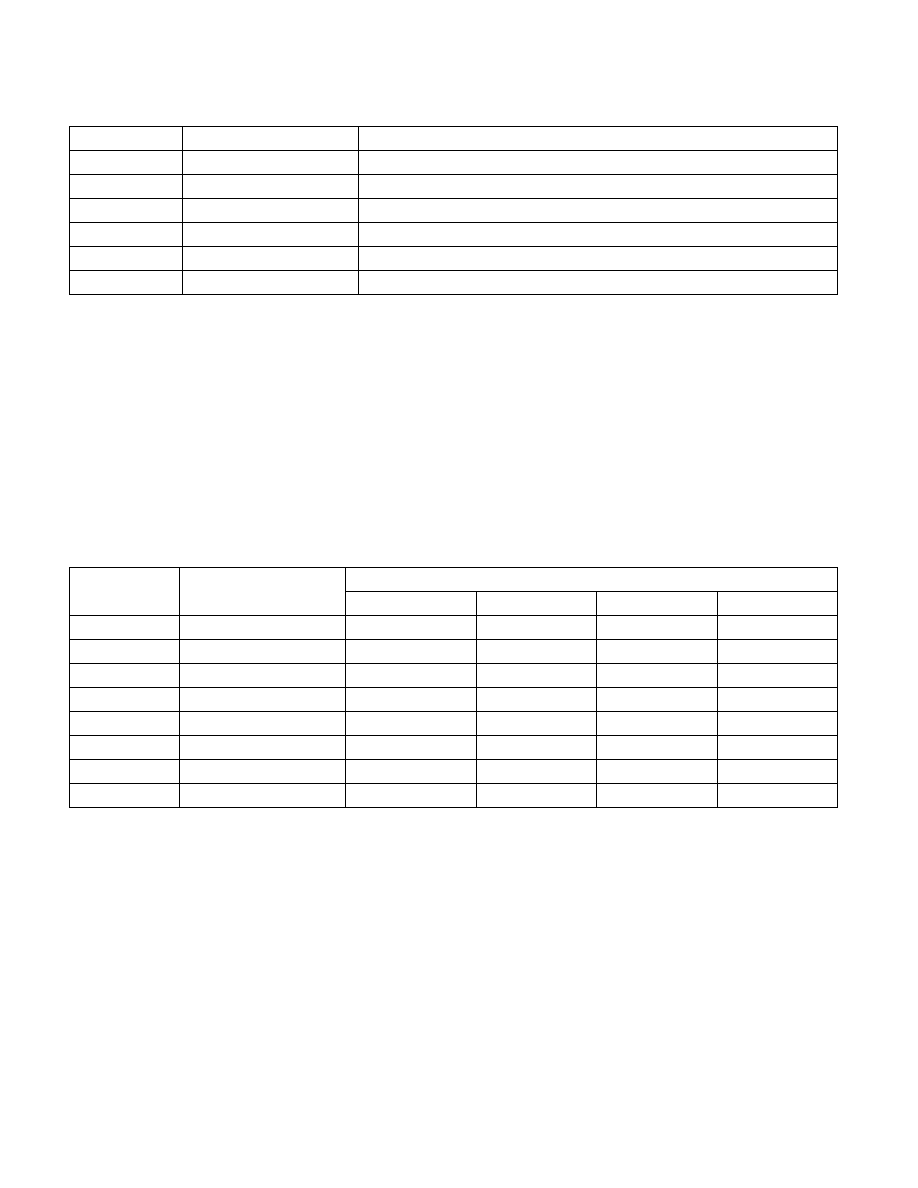

Table 36-14. An Illustrative CYC Packet Example

Time (cycles)

Instruction Snapshot

Threshold

0

16

32

64

x

jmp %eax

CYC, TIP

CYC, TIP

CYC, TIP

CYC, TIP

x + 9

call %ebx

CYC, TIP

TIP

TIP

TIP

x + 15

call %ecx

CYC, TIP

TIP

TIP

TIP

x + 30

jmp %edx

CYC, TIP

CYC, TIP

TIP

TIP

x + 38

mov cr3, %eax

CYC, PIP

PIP

CYC, PIP

PIP

x + 46

jmp [%eax]

CYC, TIP

CYC, TIP

TIP

TIP

x + 64

call %edx

CYC, TIP

CYC, TIP

TIP

CYC,TIP

x + 71

jmp %edx

CYC, TIP

TIP

CYC,TIP

TIP