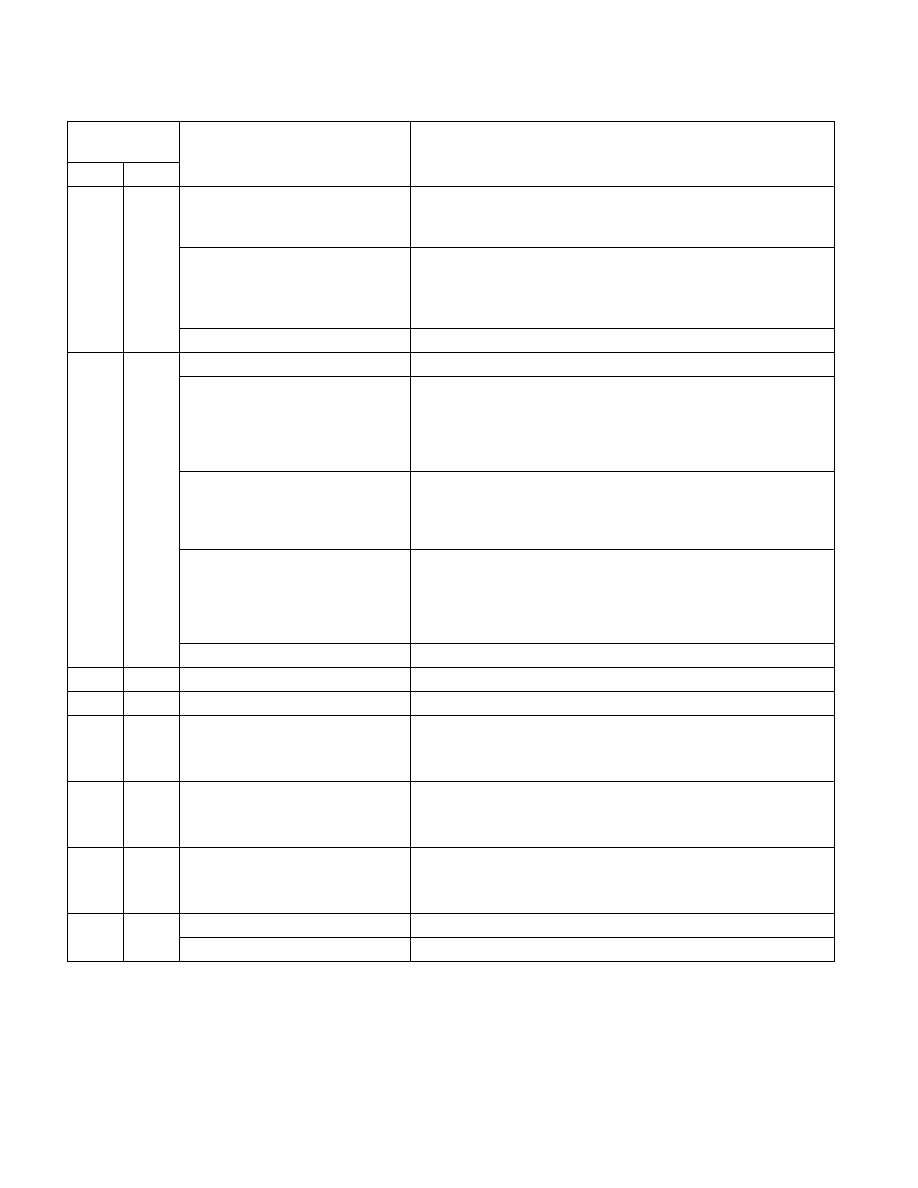

35-316 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

7:0

Count (RO)

Indicates the number of hardware unit error reporting banks available in

the processor.

8

IA32_MCG_CTL Present (RO)

1 = Indicates that the processor implements the MSR_MCG_CTL

register found at MSR 17BH.

0 = Not supported.

63:9

Reserved.

17AH

378

IA32_MCG_STATUS

0

RIPV

When set, this bit indicates that the instruction addressed by the

instruction pointer pushed on the stack (when the machine check was

generated) can be used to restart the program. If this bit is cleared, the

program cannot be reliably restarted.

1

EIPV

When set, this bit indicates that the instruction addressed by the

instruction pointer pushed on the stack (when the machine check was

generated) is directly associated with the error.

2

MCIP

When set, this bit indicates that a machine check has been generated. If a

second machine check is detected while this bit is still set, the processor

enters a shutdown state. Software should write this bit to 0 after

processing a machine check exception.

63:3

Reserved.

198H

408

IA32_PERF_STATUS

199H

409

IA32_PERF_CTL

See Table 35-2.

19AH

410

IA32_CLOCK_MODULATION

Clock Modulation (R/W).

See Table 35-2.

See Section 14.7.3, “Software Controlled Clock Modulation.”

19BH

411

IA32_THERM_INTERRUPT

Thermal Interrupt Control (R/W)

See Table 35-2.

See Section 14.7.2, “Thermal Monitor.”

19CH

412

IA32_THERM_STATUS

Thermal Monitor Status (R/W)

See Table 35-2.

See Section 14.7.2, “Thermal Monitor.”

19DH

413

MSR_THERM2_CTL

15:0

Reserved.

Table 35-45. MSRs in Pentium M Processors (Contd.)

Register

Address

Register Name

Bit Description

Hex

Dec