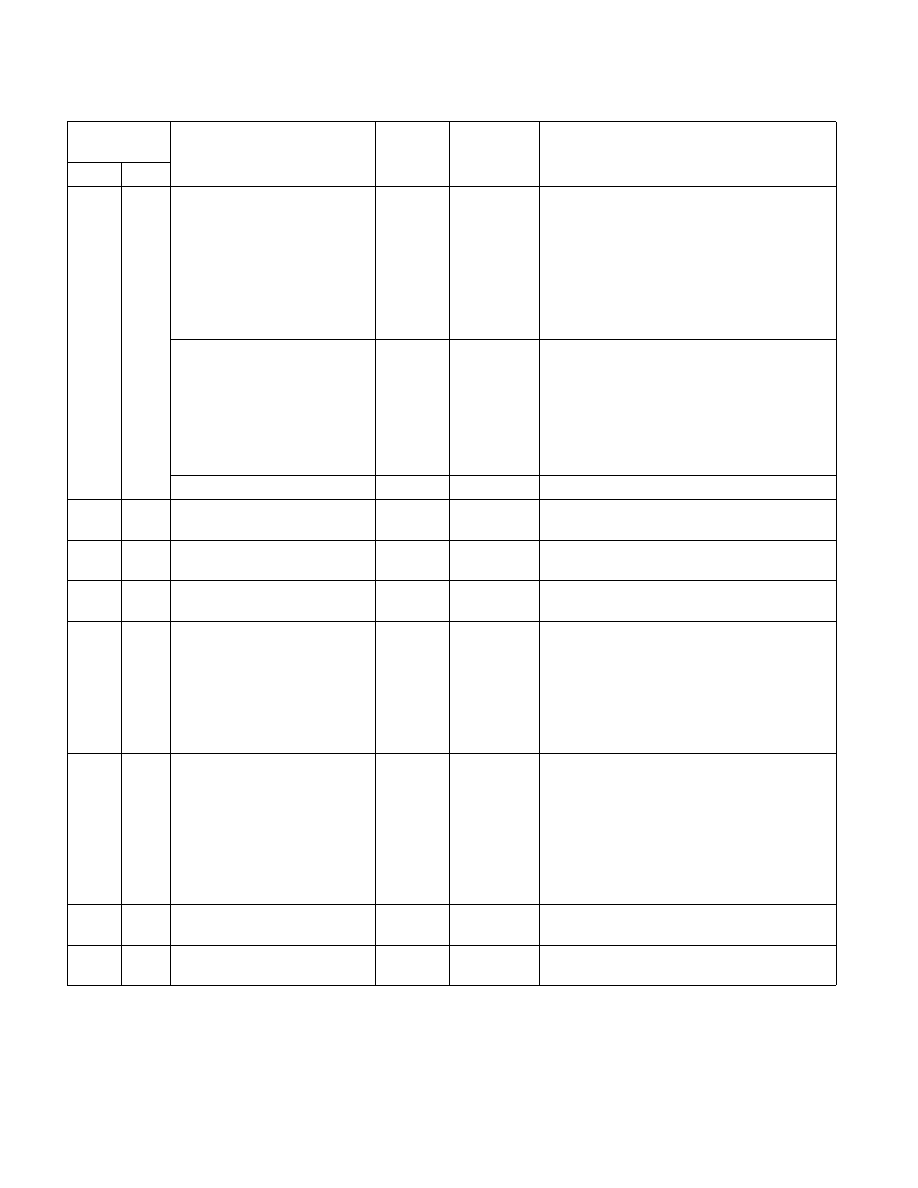

35-296 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

25

ENABLE_PEBS_MY_THR (R/W)

Enables PEBS for the target logical processor

when set; disables PEBS when clear (default).

See Section 18.13.3, ÔÇťIA32_PEBS_ENABLE MSR,ÔÇŁ

for an explanation of the target logical processor.

This bit is called ENABLE_PEBS in IA-32

processors that do not support Intel Hyper-

Threading Technology.

26

ENABLE_PEBS_OTH_THR (R/W)

Enables PEBS for the target logical processor

when set; disables PEBS when clear (default).

See Section 18.13.3, ÔÇťIA32_PEBS_ENABLE MSR,ÔÇŁ

for an explanation of the target logical processor.

This bit is reserved for IA-32 processors that do

not support Intel Hyper-Threading Technology.

63:27

Reserved.

3F2H

1010 MSR_PEBS_MATRIX_VERT

0, 1, 2, 3,

4, 6

Shared

400H

1024 IA32_MC0_CTL

0, 1, 2, 3,

4, 6

Shared

See Section 15.3.2.1, ÔÇťIA32_MCi_CTL MSRs.ÔÇŁ

401H

1025 IA32_MC0_STATUS

0, 1, 2, 3,

4, 6

Shared

See Section 15.3.2.2, ÔÇťIA32_MCi_STATUS MSRS.ÔÇŁ

402H

1026 IA32_MC0_ADDR

0, 1, 2, 3,

4, 6

Shared

See Section 15.3.2.3, ÔÇťIA32_MCi_ADDR MSRs.ÔÇŁ

The IA32_MC0_ADDR register is either not

implemented or contains no address if the ADDRV

flag in the IA32_MC0_STATUS register is clear.

When not implemented in the processor, all reads

and writes to this MSR will cause a general-

protection exception.

403H

1027 IA32_MC0_MISC

0, 1, 2, 3,

4, 6

Shared

See Section 15.3.2.4, ÔÇťIA32_MCi_MISC MSRs.ÔÇŁ

The IA32_MC0_MISC MSR is either not

implemented or does not contain additional

information if the MISCV flag in the

IA32_MC0_STATUS register is clear.

When not implemented in the processor, all reads

and writes to this MSR will cause a general-

protection exception.

404H

1028 IA32_MC1_CTL

0, 1, 2, 3,

4, 6

Shared

See Section 15.3.2.1, ÔÇťIA32_MCi_CTL MSRs.ÔÇŁ

405H

1029 IA32_MC1_STATUS

0, 1, 2, 3,

4, 6

Shared

See Section 15.3.2.2, ÔÇťIA32_MCi_STATUS MSRS.ÔÇŁ

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec