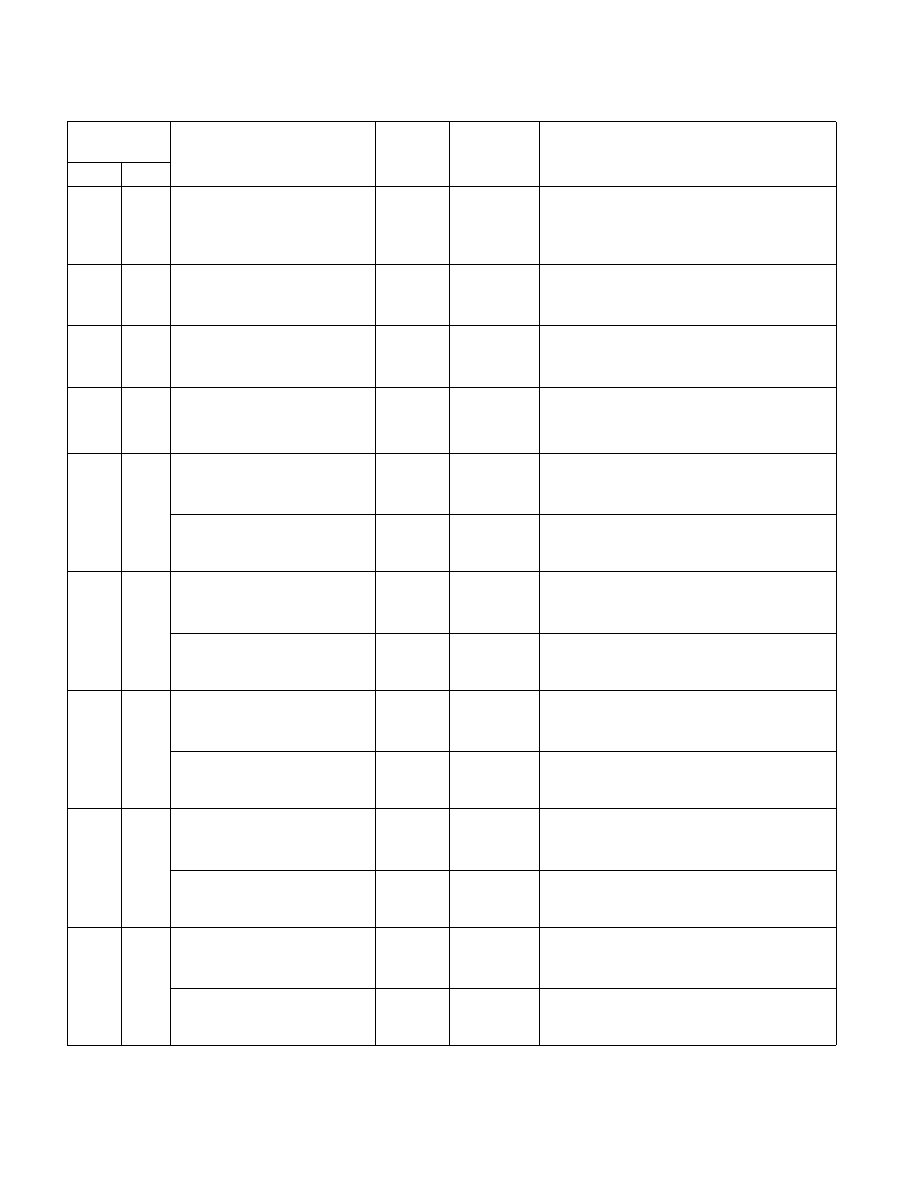

35-282 Vol. 3C

MODEL-SPECIFIC REGISTERS (MSRS)

176H

374

IA32_SYSENTER_EIP

0, 1, 2, 3,

4, 6

Unique

CPL 0 code entry point (R/W)

See Table 35-2. See Section 5.8.7, “Performing

Fast Calls to System Procedures with the

SYSENTER and SYSEXIT Instructions.”

179H

377

IA32_MCG_CAP

0, 1, 2, 3,

4, 6

Unique

Machine Check Capabilities (R)

See Table 35-2. See Section 15.3.1.1,

17AH

378

IA32_MCG_STATUS

0, 1, 2, 3,

4, 6

Unique

Machine Check Status. (R)

See Table 35-2. See Section 15.3.1.2,

17BH

379

IA32_MCG_CTL

Machine Check Feature Enable (R/W)

See Table 35-2.

See Section 15.3.1.3, “IA32_MCG_CTL MSR.”

180H

384

MSR_MCG_RAX

0, 1, 2, 3,

4, 6

Unique

Machine Check EAX/RAX Save State

See Section 15.3.2.6, “IA32_MCG Extended

63:0

Contains register state at time of machine check

error. When in non-64-bit modes at the time of

the error, bits 63-32 do not contain valid data.

181H

385

MSR_MCG_RBX

0, 1, 2, 3,

4, 6

Unique

Machine Check EBX/RBX Save State

See Section 15.3.2.6, “IA32_MCG Extended

63:0

Contains register state at time of machine check

error. When in non-64-bit modes at the time of

the error, bits 63-32 do not contain valid data.

182H

386

MSR_MCG_RCX

0, 1, 2, 3,

4, 6

Unique

Machine Check ECX/RCX Save State

See Section 15.3.2.6, “IA32_MCG Extended

63:0

Contains register state at time of machine check

error. When in non-64-bit modes at the time of

the error, bits 63-32 do not contain valid data.

183H

387

MSR_MCG_RDX

0, 1, 2, 3,

4, 6

Unique

Machine Check EDX/RDX Save State

See Section 15.3.2.6, “IA32_MCG Extended

63:0

Contains register state at time of machine check

error. When in non-64-bit modes at the time of

the error, bits 63-32 do not contain valid data.

184H

388

MSR_MCG_RSI

0, 1, 2, 3,

4, 6

Unique

Machine Check ESI/RSI Save State

See Section 15.3.2.6, “IA32_MCG Extended

63:0

Contains register state at time of machine check

error. When in non-64-bit modes at the time of

the error, bits 63-32 do not contain valid data.

Table 35-41. MSRs in the Pentium® 4 and Intel® Xeon® Processors (Contd.)

Register

Address

Register Name

Fields and Flags

Model

Avail-

ability

Shared/

Unique

1

Bit Description

Hex

Dec