15-4 Vol. 3B

MACHINE-CHECK ARCHITECTURE

ŌĆó

MCG_LMCE_P (local machine check exception) flag, bit 27 ŌĆö Indicates (when set) that the following

interfaces are present:

ŌĆö an extended state LMCE_S (located in bit 3 of IA32_MCG_STATUS), and

ŌĆö the IA32_MCG_EXT_CTL MSR, necessary to support Local Machine Check Exception (LMCE).

A non-zero MCG_LMCE_P indicates that, when LMCE is enabled as described in Section 15.3.1.5, some machine

check errors may be delivered to only a single logical processor.

The effect of writing to the IA32_MCG_CAP MSR is undefined.

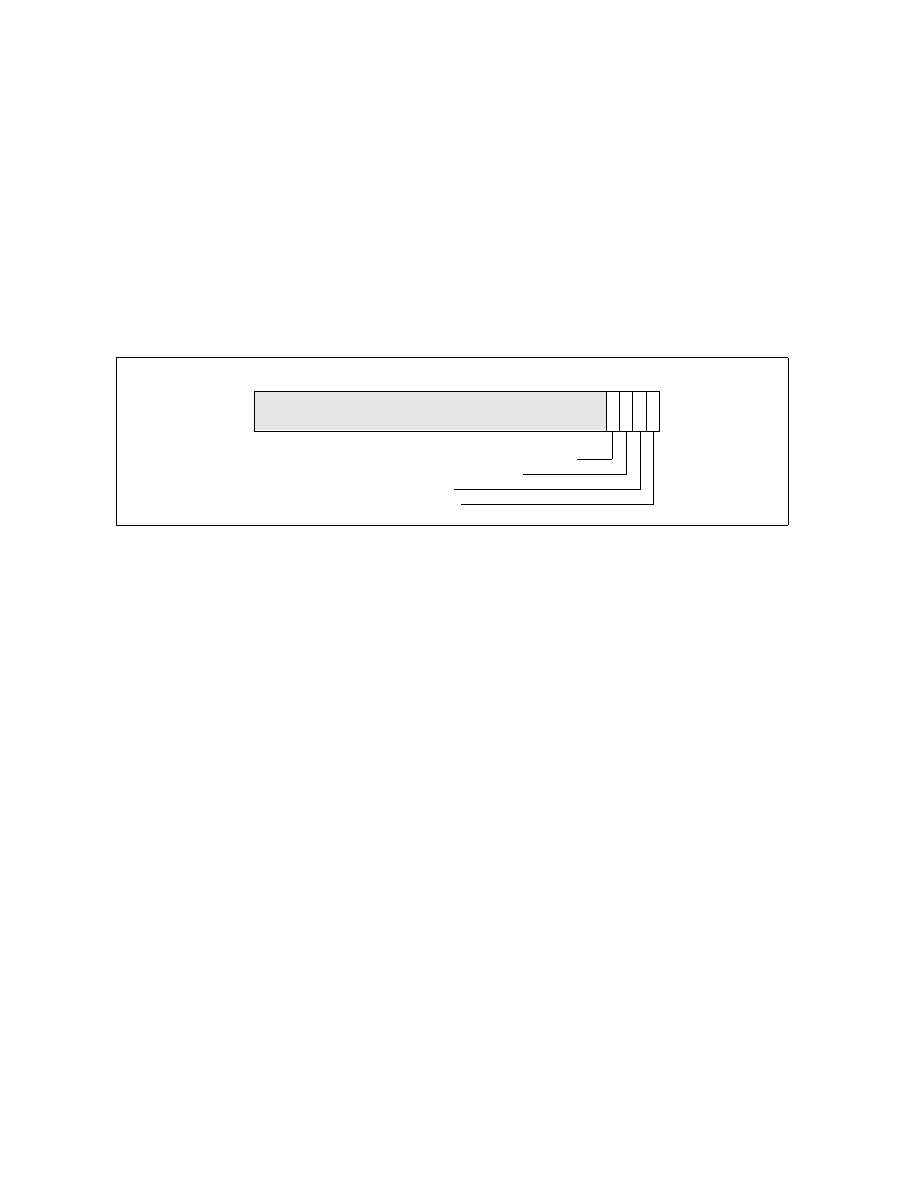

15.3.1.2 IA32_MCG_STATUS MSR

The IA32_MCG_STATUS MSR describes the current state of the processor after a machine-check exception has

occurred (see Figure 15-3).

Where:

ŌĆó

RIPV (restart IP valid) flag, bit 0 ŌĆö Indicates (when set) that program execution can be restarted reliably

at the instruction pointed to by the instruction pointer pushed on the stack when the machine-check exception

is generated. When clear, the program cannot be reliably restarted at the pushed instruction pointer.

ŌĆó

EIPV (error IP valid) flag, bit 1 ŌĆö Indicates (when set) that the instruction pointed to by the instruction

pointer pushed onto the stack when the machine-check exception is generated is directly associated with the

error. When this flag is cleared, the instruction pointed to may not be associated with the error.

ŌĆó

MCIP (machine check in progress) flag, bit 2 ŌĆö Indicates (when set) that a machine-check exception was

generated. Software can set or clear this flag. The occurrence of a second Machine-Check Event while MCIP is

set will cause the processor to enter a shutdown state. For information on processor behavior in the shutdown

state, please refer to the description in Chapter 6, ŌĆ£Interrupt and Exception HandlingŌĆØ: ŌĆ£Interrupt 8ŌĆöDouble

Fault Exception (#DF)ŌĆØ.

ŌĆó

LMCE_S (local machine check exception signaled), bit 3 ŌĆö Indicates (when set) that a local machine-

check exception was generated. This indicates that the current machine-check event was delivered to only this

logical processor.

Bits 63:04 in IA32_MCG_STATUS are reserved. An attempt to write to IA32_MCG_STATUS with any value other

than 0 would result in #GP.

15.3.1.3 IA32_MCG_CTL MSR

The IA32_MCG_CTL MSR is present if the capability flag MCG_CTL_P is set in the IA32_MCG_CAP MSR.

IA32_MCG_CTL controls the reporting of machine-check exceptions. If present, writing 1s to this register enables

machine-check features and writing all 0s disables machine-check features. All other values are undefined and/or

implementation specific.

Figure 15-3. IA32_MCG_STATUS Register

EIPVŌĆöError IP valid flag

MCIPŌĆöMachine check in progress flag

63

0

Reserved

1

2

3

E

I

P

V

M

C

I

P

R

I

P

V

RIPVŌĆöRestart IP valid flag

LMCE_SŌĆöLocal machine check exception signaled